### UC Riverside UC Riverside Electronic Theses and Dissertations

### Title

Hashing, Caching, and Synchronization: Memory Techniques for Latency Masking Multithreaded Applications

**Permalink** https://escholarship.org/uc/item/2rs9f9pg

**Author** Windh, Skyler Arron

Publication Date 2018

### **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA RIVERSIDE

Hashing, Caching, and Synchronization: Memory Techniques for Latency Masking Multithreaded Applications

> A Dissertation submitted in partial satisfaction of the requirements for the degree of

> > Doctor of Philosophy

in

Computer Science

by

Skyler Arron Windh

September 2018

Dissertation Committee:

Dr. Walid A. Najjar, Chairperson Dr. Vassilis Tsotras Dr. Nael Abu-Ghazaleh Dr. Daniel Wong

Copyright by Skyler Arron Windh 2018 The Dissertation of Skyler Arron Windh is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

Looking back on the last six years of my Ph.D., it has been a time of tremendous growth. Both personally and professionally. And that growth comes from both great accomplishments and deep, deep upsets. I am forever grateful to my advisor Dr. Walid Najjar for the man he has been in my life. He has been a constant source of wisdom both technical and personal. He has given my work direction and kept me steady when life gave me punches.

I would also like to thank Dr. Vassilis Tsotras for his assistance on my work the last few years. He has been very helpful in editing papers and asking questions that keep projects in scope. I also thank my other committee members, Dr. Nael Abu-Ghazaleh and Dr. Daniel Wong for their time serving on my committee and for asking good questions that lead to exploring different avenues in this research.

During graduate school, I learned as much about life and personal skills as I did technical. Thank you Steven Jacobs for jumping into grad school with me because why not. I'm grateful to all the friends I have made in the Embedded Systems lab and all the help I have received. Thanks to Robert Halstead who showed me the ropes with FPGAs and left a lot of fertile research for me to pursue. Prerna Budhkar and I have spent many hours hashing out details of this multithreaded model and how it would work in many different applications. Her patient, hard-working demeanor is inspiring and a goal I hope to reach one day. Jose Rodriguez has been a good friend and colleague, always willing to let me bounce ideas off of him and see what solutions fall out. And my good friend Jason Ott, who spent many hours with me discussing faith, physics, fatherhood, and so many other random topics. Thanks for the encouragement and friendship. Finally, this thesis contains two of my previously published works from my research. The first explores HLS tools and was published in The Proceedings of the IEEE. I want to thank the reviewers and publishers for considering the work as well as my coauthors for the help in bringing it all together. It's content appears in Chapter 3.The full citation and author list is as follows:

Skyler Windh, Xiaoyin Ma, Robert J Halstead, Prerna Budhkar, Zabdiel Luna, Omar Hussaini, and Walid A Najjar. High-level Language Tools for Reconfigurable Computing. Proceedings of the IEEE, 103(3):390-408, 2015.

The other paper was published at ICCAD in 2015 and applied our multithreaded model to breadth first search. It's content is the basis for Chapter 4. The full citation is:

Skyler Windh, Prerna Budhkar, and Walid A. Najjar. CAMs as Synchronizing Caches for Multithreaded Irregular Applications on FPGAs. ICCAD'15, pages 331-336, 2015. To my parents for all the years of support and encouragement.

To my amazing wife Melanie, thanks for the never-ending support through the hardest parts. I would not have finished without you and your constant selflessness.

To my children. May this always encourage you to work hard and persevere.

#### ABSTRACT OF THE DISSERTATION

#### Hashing, Caching, and Synchronization: Memory Techniques for Latency Masking Multithreaded Applications

by

Skyler Arron Windh

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, September 2018 Dr. Walid A. Najjar, Chairperson

The increase in size and decrease in cost of DRAMs has led to a rapid growth of in-memory solutions to data analytics. In this area, performance is often limited by the latency and bandwidth of the memory system. Furthermore, the move to multicore execution has put added pressure on the memory bandwidth and often results in additional latency.

Irregular applications, by their very nature, suffer from poor data locality. This often results in high miss rates for caches and many long waits to off-chip memory. Historically, long latencies have been dealt with in two ways: (1) latency mitigation using large cache hierarchies, or (2) latency masking where threads relinquish their control after issuing a memory request. Multithreaded CPUs are designed for a fixed maximum number of threads tailored for an average application. FPGAs, however, can be customized to specific applications. Their massive parallelism is well known, and ideally suited to dynamically manage hundreds, or thousands, of threads. Multithreading, in essence, trades memory bandwidth for latency. This thesis describes the use of CAMs (Content Addressable Memories) as synchronizing caches for hardware multithreading. We demonstrate and evaluate this mechanism by implementing multithreaded datapaths for Breadth First Search, Hash-Join, and Group-By Aggregation. Synchronization between concurrent threads is typically implemented using expensive in-memory locks that are accessed via atomic operations. CAMs allow us to move the lock on chip, increase the multithreading, and achieve better performance.

# Contents

| List of Figures |       |                                                     | xii |  |

|-----------------|-------|-----------------------------------------------------|-----|--|

| Li              | st of | Tables                                              | xiv |  |

| 1               | Intr  | roduction                                           | 1   |  |

| 2 Background    |       | kground                                             | 5   |  |

|                 | 2.1   | Multithreaded Architectures                         | 5   |  |

|                 |       | 2.1.1 Temporal Multithreading                       | 7   |  |

|                 | 2.2   | Latency Masking Multithreaded Architectures         | 8   |  |

|                 | 2.3   | MT-FPGA Execution Model                             | 9   |  |

|                 | 2.4   | FPGA Heterogeneous Computing                        | 13  |  |

|                 | 2.5   | Convey HC-2ex Platform                              | 14  |  |

|                 | 2.6   | CAMs on FPGA                                        | 16  |  |

|                 | 2.7   | Query Processing on FPGAs                           | 18  |  |

| 3               | Hig   | h Level Language Tools for Reconfigurable Computing | 21  |  |

| -               | 3.1   | High Level Synthesis and FPGAs                      | 22  |  |

|                 | -     | 3.1.1 A Historical Perspective                      | 25  |  |

|                 |       | 3.1.2 Hardware and Software Computing Models        | 27  |  |

|                 | 3.2   | Related Work                                        | 32  |  |

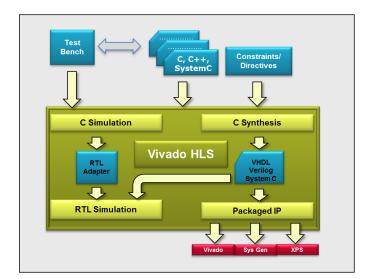

|                 | 0.2   | 3.2.1 Xilinx Vivado HLS                             | 33  |  |

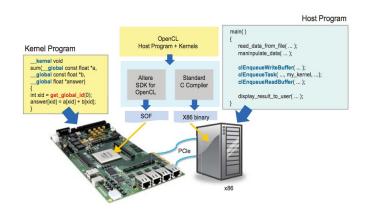

|                 |       | 3.2.2 Altera OpenCL                                 | 35  |  |

|                 |       | 3.2.3 Bluespec System Verilog                       | 39  |  |

|                 |       | 3.2.4 LegUp 3.0 (U. Toronto)                        | 44  |  |

|                 |       | 3.2.5 ROCCC 2.0 (UC Riverside)                      | 47  |  |

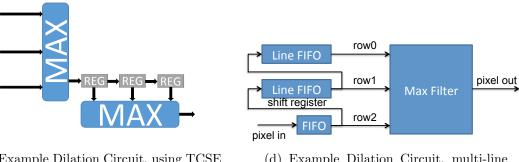

|                 | 3.3   | Dilation Kernel Example                             | 49  |  |

|                 |       | 3.3.1 CPU Implementation                            | 53  |  |

|                 |       | 3.3.2 Vivado HLS                                    | 55  |  |

|                 |       | 3.3.3 OpenCL                                        | 56  |  |

|                 |       | 3.3.4 Bluespec System Verilog                       | 57  |  |

|                 |       | 3.3.5 LegUp 3.0                                     | 60  |  |

|                 |       |                                                     |     |  |

|          |                | 3.3.6 ROCCC 2.0                                                |

|----------|----------------|----------------------------------------------------------------|

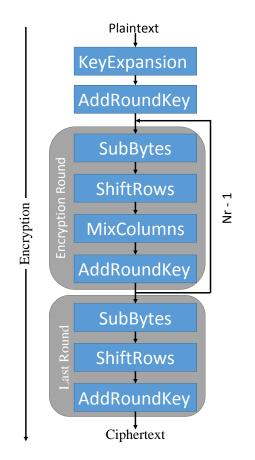

|          | 3.4            | AES Encryption Kernel Example                                  |

|          |                | 3.4.1 Implementing AES                                         |

|          | 3.5            | Synthesis Results                                              |

|          |                | 3.5.1 Pass-Through Filter                                      |

|          |                | 3.5.2 Area Utilization                                         |

|          |                | 3.5.3 Runtime Performance                                      |

|          |                | 3.5.4 AES Performance and Power                                |

|          | 3.6            | Conclusion                                                     |

| 4        | CA             | Ms as Synchronizing Caches for Multithreaded Workloads 71      |

| •        | 4.1            | Accelerating Breadth First Search                              |

|          | 4.2            | Hardware Multithreaded Breadth First Search                    |

|          | 4.3            | Implementation     77                                          |

|          | 4.4            | Experimental Evaluation                                        |

|          | 4.5            | Conclusion   81                                                |

|          | 1.0            |                                                                |

| <b>5</b> | $\mathbf{Pro}$ | cessor-Side Locking for FPGA Multithreading of In-Memory Hash- |

|          | bas            | ed Operators 83                                                |

|          | 5.1            | Related Work                                                   |

|          |                | 5.1.1 Hash-Join                                                |

|          |                | 5.1.2 Aggregation                                              |

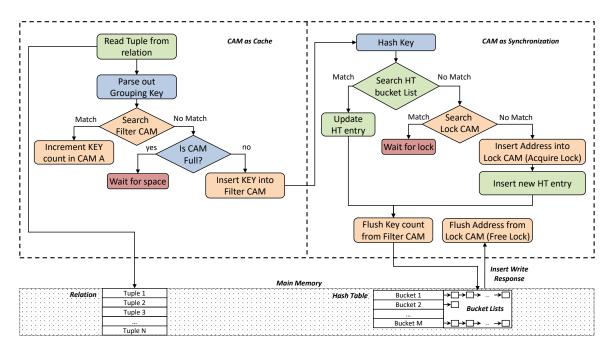

|          | 5.2            | Group-By Aggregation on FPGA                                   |

|          |                | 5.2.1 Fine Grained Locking                                     |

|          |                | 5.2.2 Aggregation Engine Workflow                              |

|          |                | 5.2.3 FPGA Design Optimizations & Trade-offs                   |

|          | 5.3            | Experimental Results                                           |

|          |                | 5.3.1 Software Implementations                                 |

|          |                | 5.3.2 Dataset description                                      |

|          |                | 5.3.3 Effect of Filter CAM size 100                            |

|          |                | 5.3.4 Throughput Evaluation                                    |

|          |                | 5.3.5 Effects of the Merge Operation                           |

|          |                | 5.3.6 FPGA Area Utilization                                    |

|          | 5.4            | Hash Join using CAMs                                           |

|          | -              | 5.4.1 Build Phase Engine 110                                   |

|          |                | 5.4.2 Probe Phase Engine                                       |

|          |                | 5.4.3 Possible Optimizations                                   |

|          |                | 5.4.4 Experimental Results                                     |

|          | 5.5            | Hash Join with Arbitrary Size Tuples                           |

|          |                | 5.5.1 Supporting Variable Tuple Lengths                        |

|          |                | 5.5.2 Increasing the Key/Value Size                            |

|          |                | 5.5.3 Adjustments to software approaches                       |

|          |                | 5.5.4 Experimental Results                                     |

|          | 5.6            | Conclusions                                                    |

|          | 0.0            |                                                                |

| 6  | 6 Better Building Blocks |        |                      |       |   |

|----|--------------------------|--------|----------------------|-------|---|

|    | 6.1                      | Improv | ving CAM Performance | . 139 | 9 |

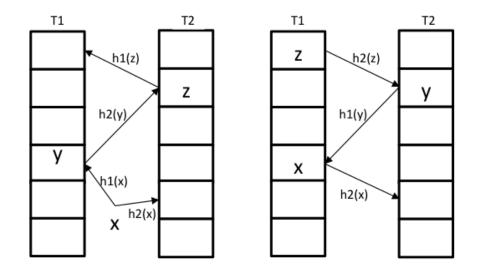

|    | 6.2                      | Cucko  | o Hashing            | . 14  | 1 |

|    |                          | 6.2.1  | Related Work         | . 142 | 2 |

|    |                          | 6.2.2  | Implementation       | . 14  | 4 |

| 7  | 7 Conclusions            |        | 14                   | 6     |   |

| Bi | Bibliography 1           |        |                      |       |   |

# List of Figures

| 1.1  | The Memory Wall   2                                                                                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1  | Various multithreading models                                                                                                                                            |

| 2.2  | Hiding Memory Latency                                                                                                                                                    |

| 2.3  | MT-FPGA Architecture Model                                                                                                                                               |

| 2.4  | Understanding MT-FPGA Throughput 12                                                                                                                                      |

| 2.5  | The Convey HC-2ex architecture                                                                                                                                           |

| 3.1  | xkcd: Compiling                                                                                                                                                          |

| 3.2  | Architecture of the DEC PReL PAM $P_0$                                                                                                                                   |

| 3.3  | Vivado HLS Workflow                                                                                                                                                      |

| 3.4  | The OpenCL system overview, image from [118]                                                                                                                             |

| 3.5  | Sample OpenCL kernel function with programmer set attributes                                                                                                             |

| 3.6  | OpenCL compiler optimization techniques to increase parallelism                                                                                                          |

| 3.7  | Multiplication example in BSV                                                                                                                                            |

| 3.8  | Scheduling of Rules in BSV 43                                                                                                                                            |

| 3.9  | LegUp 3.0 Target Architecture                                                                                                                                            |

| 3.10 | Assume WIDTH and HEIGHT are defined in terms of filter size. A sim-                                                                                                      |

|      | ple change to access pattern and order of calculations makes a significant                                                                                               |

|      | difference for CPU optimization opportunities                                                                                                                            |

|      | Dilation Example                                                                                                                                                         |

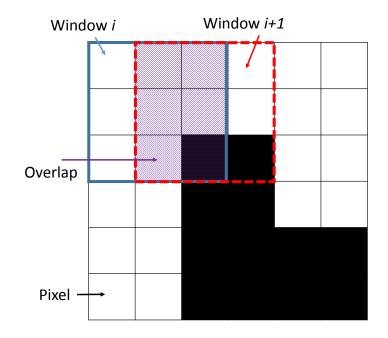

| 3.12 | Examples of Naïve implementations(Top) vs. Smart optimizations(Bottom) 51                                                                                                |

| 3.13 | Overlapping region of adjacent Dilation windows can lead to smart optimiza-                                                                                              |

|      | tion or redundant memory requests $\ldots \ldots \ldots$ |

|      | OpenCL implementation of Dilation using a single loop structure                                                                                                          |

| 3.15 | BSV Interface to dilation module                                                                                                                                         |

| 3.16 | Dilation implementation in BSV                                                                                                                                           |

| 3.17 | AES Flow Graph                                                                                                                                                           |

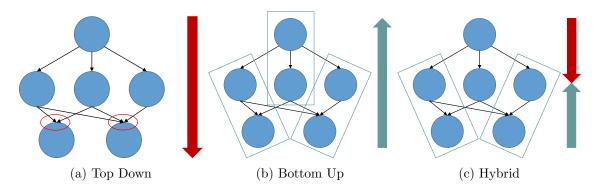

| 4.1  | The three main approaches to the Breadth First Search algorithm                                                                                                          |

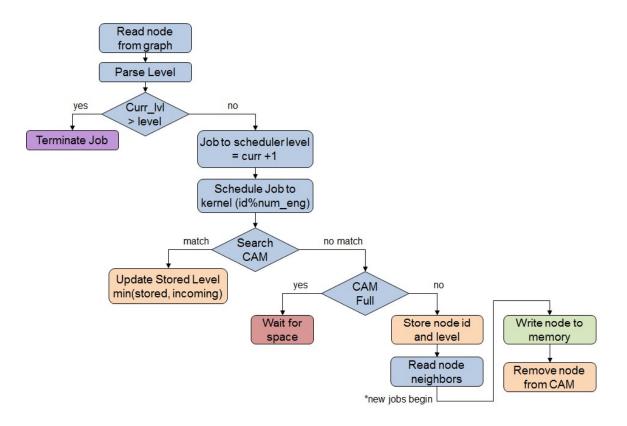

| 4.2  | BFS Thread Flow                                                                                                                                                          |

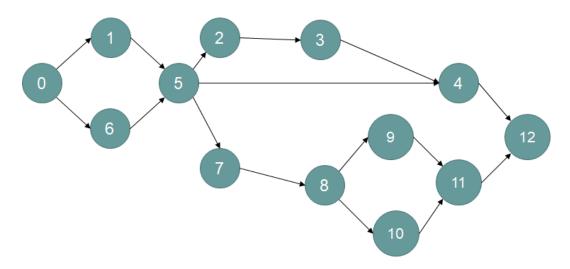

| 4.3  | BFS Example Graph                                                                                                                                                        |

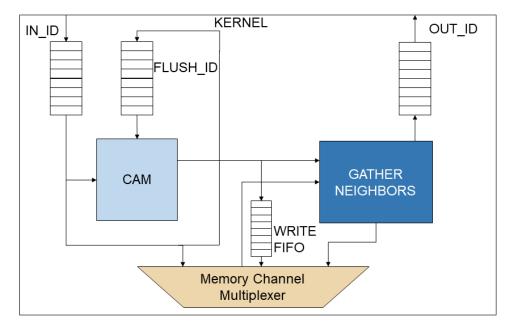

| $4.4 \\ 4.5$ | BFS Engine Layout                                                                                                                                         | $\frac{78}{79}$ |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 5 1          |                                                                                                                                                           | 89              |

| $5.1 \\ 5.2$ | Multithreaded Architecture details $\ldots$                              | - 89<br>- 90    |

| 5.2<br>5.3   | A state diagram for jobs in the aggregation engine                                                                                                        | 90<br>92        |

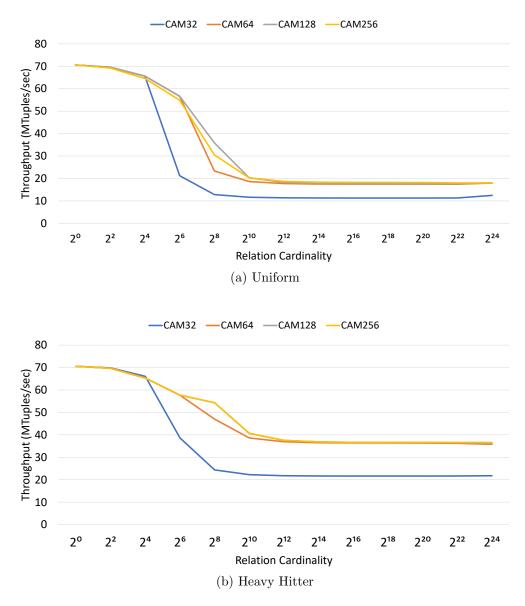

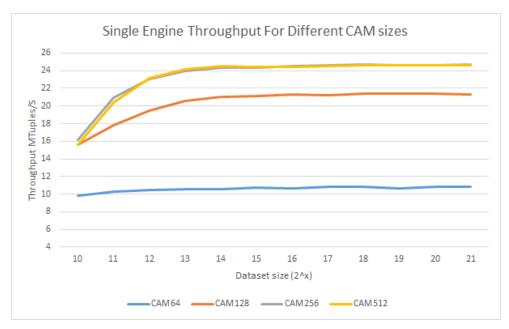

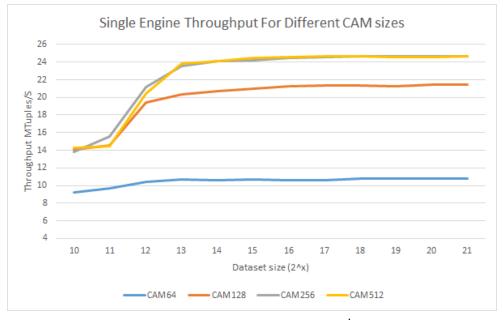

| $5.3 \\ 5.4$ | Aggregation throughput of single engine for 256M tuples as <i>Filter CAM</i> size                                                                         | 92              |

| 0.4          | is changed.                                                                                                                                               | 101             |

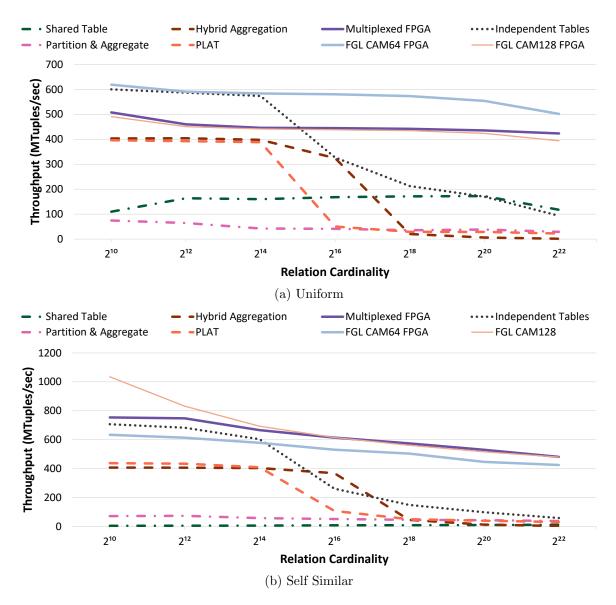

| 5.5          | Aggregation throughput for uniform and self similar datasets with 256M tuples                                                                             |                 |

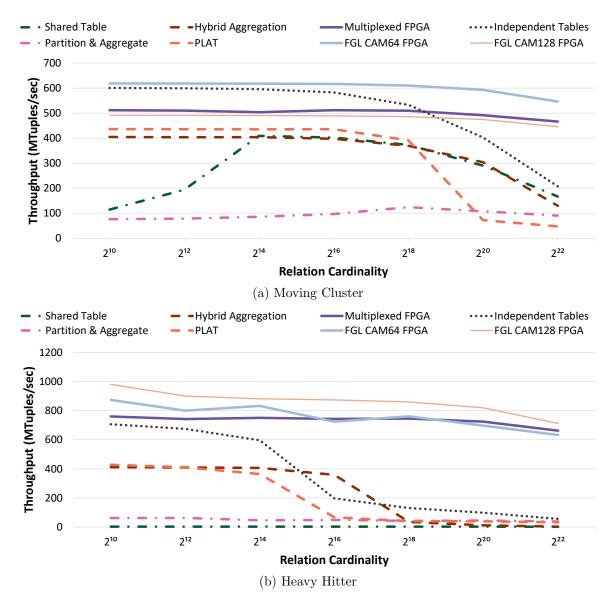

| 5.6          | Aggregation throughput for moving cluster and heavy hitter datasets with                                                                                  |                 |

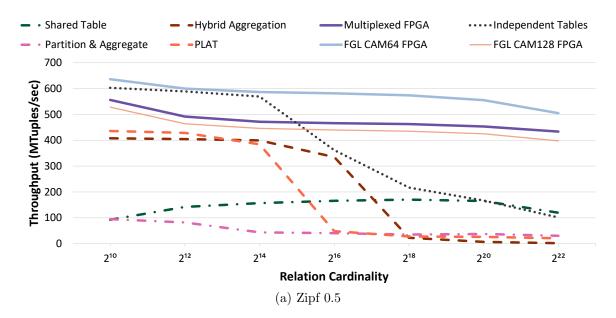

| 57           | 256M tuples                                                                                                                                               | 104             |

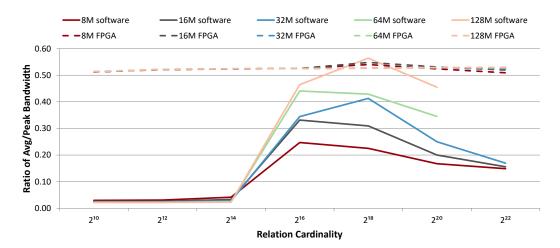

| $5.7 \\ 5.8$ | Aggregation throughput for moving Zipf 0.5 datasets with 256M tuples<br>Ratio of average effective memory bandwidth to peak theoretical bandwidth         | 105             |

|              | achieved by the Independent Tables software algorithm and the FGL CAM64                                                                                   | 107             |

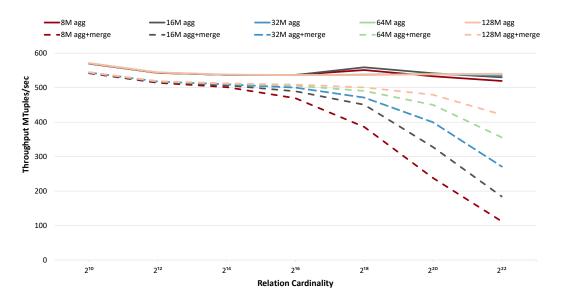

| FO           | design with 8 engines per FPGA for varying dataset sizes and key cardinalities<br>Effect of conving relation sizes on the EPCA approaching throughput for | .107            |

| 5.9          | Effect of varying relation sizes on the FPGA aggregation throughput for datasets with Uniform key distribution. Solid lines represent throughput of       |                 |

|              | the aggregation step (without merge operation), while dashed lines represent                                                                              |                 |

|              | end-to-end (aggregation followed by the merge) throughput                                                                                                 | 108             |

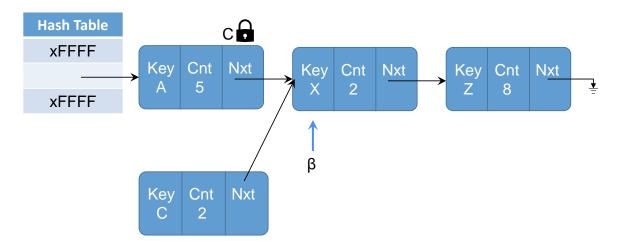

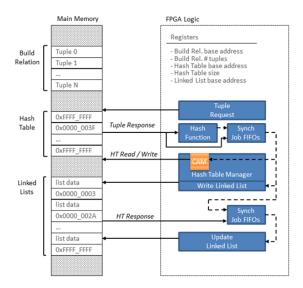

| 5 10         | The FPGA Build Phase Engine.                                                                                                                              | 111             |

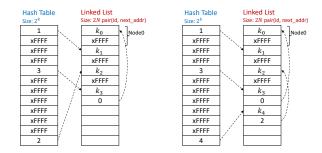

|              | Inserting an element into the Hash Table. Dashed lines represent logi-                                                                                    | 111             |

| 0.11         | cal connections. Assume $hash(k_4) = k - 1$ . Address 2 is read from the                                                                                  |                 |

|              | $hash\_table[k-1]$ and 4 is written in its place. $k_4$ is written to the 8th slot,                                                                       | 110             |

| F 19         | and the old address 2 is written as it's next pointer in the 9th slot                                                                                     | 113             |

|              | The FPGA Probe Phase Engine.                                                                                                                              | 114<br>121      |

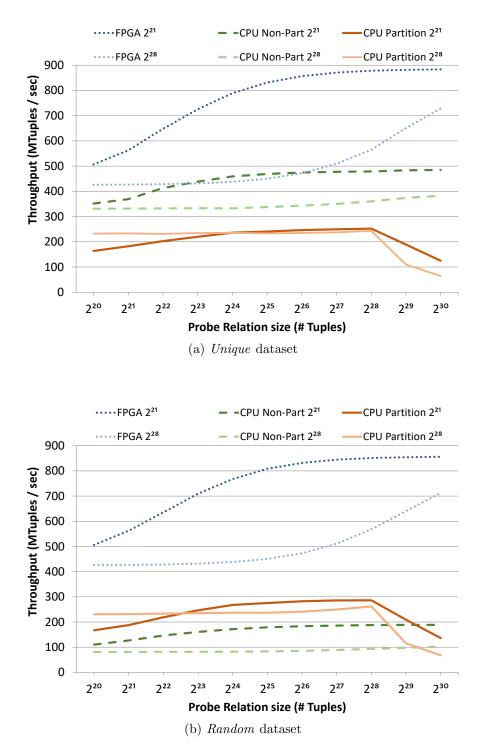

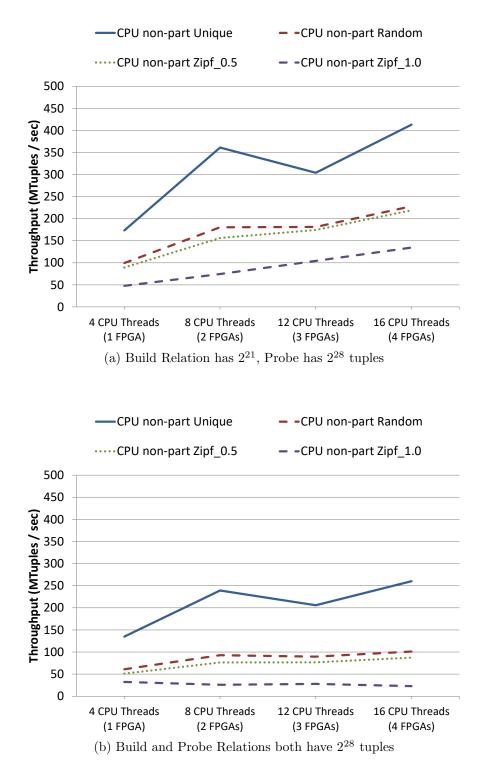

|              | Unique and Random throughput as the build relation size is increased<br>Zipf throughput as the build relation size is increased                           | $121 \\ 122$    |

|              | FPGA Throughput comparison as the bandwidth and number of threads are                                                                                     | 122             |

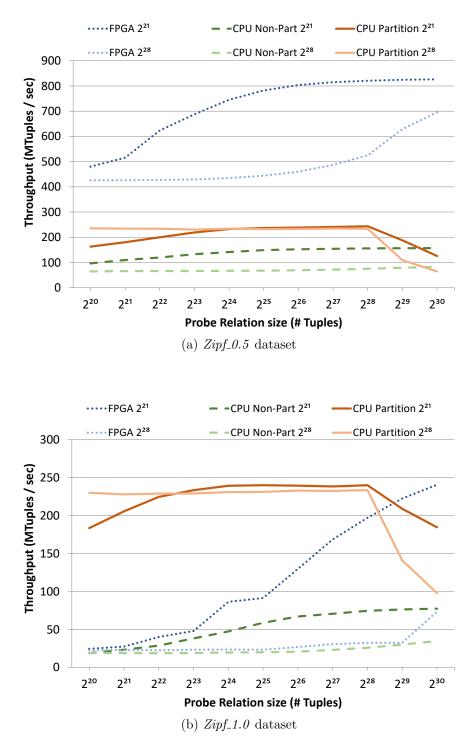

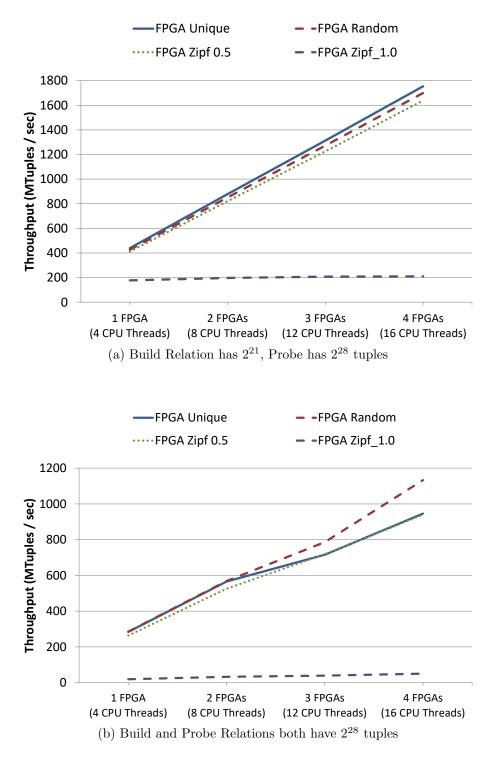

| 0.10         | increased                                                                                                                                                 | 126             |

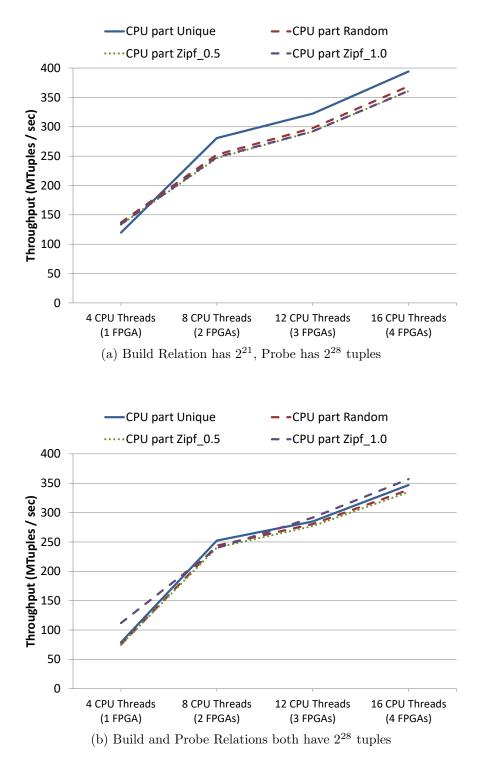

| 5.16         | Partitioned CPU throughput comparison as the bandwidth and number of                                                                                      | 120             |

| 0.10         | threads are increased                                                                                                                                     | 127             |

| 5.17         | Non-partitioned CPU throughput comparison as the bandwidth and number                                                                                     |                 |

|              | of threads are increased.                                                                                                                                 | 128             |

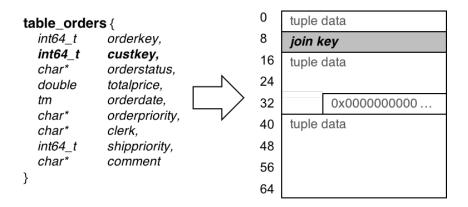

| 5.18         | Wide tuples are stored as contiguous memory blocks, but the join operation                                                                                |                 |

|              | only needs the key value. Its offset can be computed at runtime                                                                                           | 129             |

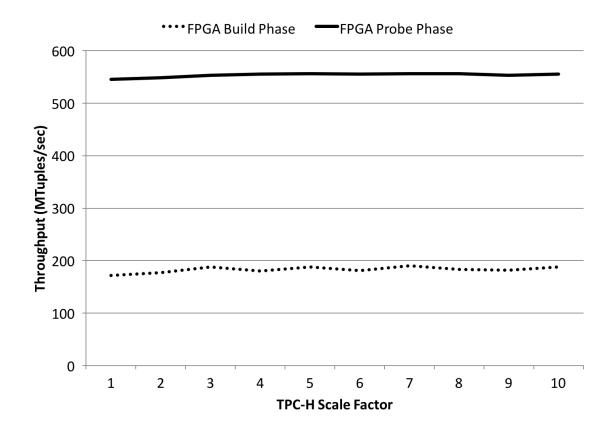

| 5.19         | FPGA throughput results for the build and probe phases as the TPC-H scale                                                                                 |                 |

|              | factor is increased.                                                                                                                                      | 134             |

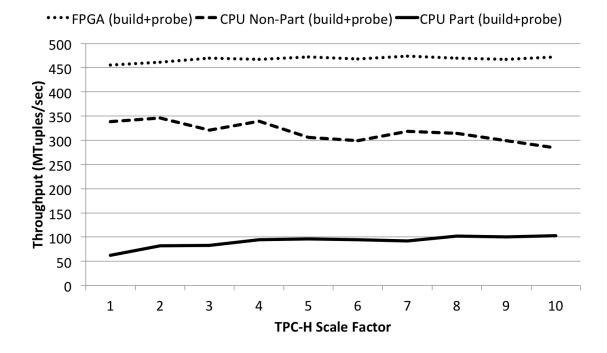

| 5.20         | FPGA and CPU total throughput performance as the TPC-H scale factor is                                                                                    |                 |

|              | increased. Results include both the build and probe phase execution times.                                                                                |                 |

|              | The partitioned CPU performance also includes the preprocessing time                                                                                      | 135             |

| 6.2          | Pipelined CAM layout                                                                                                                                      | 141             |

| 6.3          | Inserting item into a cuckoo hash table                                                                                                                   | 143             |

| 6.4          | Cuckoo Hash Software Model interface                                                                                                                      | 145             |

# List of Tables

| 3.1 | Architecture parameters of the SPLASH 1 and SPLASH 2 accelerators                | 26  |

|-----|----------------------------------------------------------------------------------|-----|

| 3.2 | Features and characteristics of Stored Program and Spatial computation models    | 30  |

| 3.3 | Area utilization and timing results for the pass-through filter                  | 65  |

| 3.4 | Dilation area utilization                                                        | 67  |

| 3.5 | Dilation runtime performance                                                     | 68  |

| 3.6 | AES Encryption Steps - Area, Frequency, and Power                                | 69  |

| 3.7 | Summary of tools features                                                        | 70  |

| 4.1 | Throughput and merged jobs for BFS on various graphs with 8 FPGA kernels         | 80  |

| 4.2 | FPGA Resource utilization.                                                       | 81  |

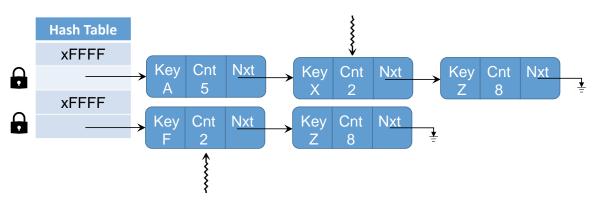

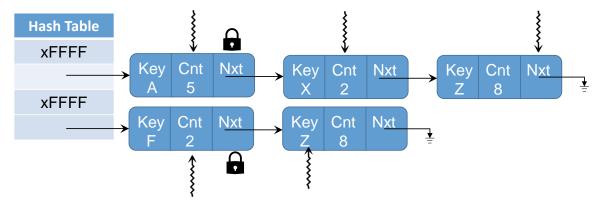

| 5.1 | Contents of the Filter CAM, Lock CAM and HashTable (HT) and modifica-            |     |

|     | tions altering all of them, while relation with the following keys is processed: |     |

|     | A, C, A, B, A. Assume hash(A)=hash(C). Initially both CAMs are empty.            |     |

|     | Filter CAM maintains the occurrence of duplicate keys, while Lock CAM            |     |

|     | locks linked-list next pointers                                                  | 93  |

| 5.2 |                                                                                  | 109 |

### Chapter 1

## Introduction

Fast database analytics over large collections of customer data is key concern for any modern business, looking to get an edge over its competitors. In recent years many companies have sprung up offering their own in-memory database solutions. Oracle's Exadata [106], and Pivotal Software's Greenplum [60] have built custom machines for memory intensive workloads. On the other hand IBM's Netezza [75], and Teradata's Kickfire [81] approached the problem using off the shelf reprogrammable hardware, i.e. integrated FPGA boards.

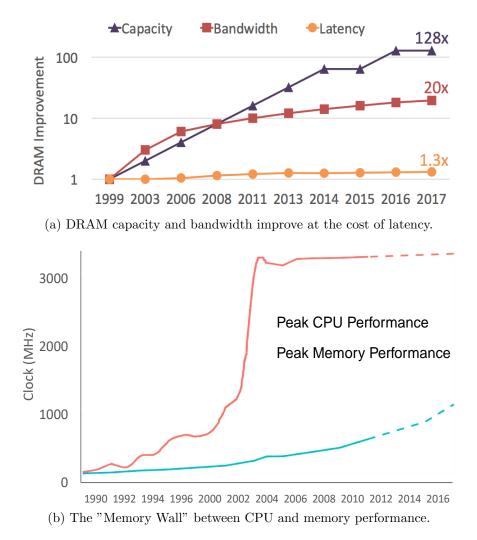

The proliferation of these solutions is to try and solve the problem of the giant gulf between our data and compute. In the Big Data era, we are producing data at tremendous rates and our compute has gotten faster than it has ever been. Yet, we still cannot feed the compute cores fast enough for all algorithms. Despite the progress made in multi-core architectures, the major performance limitations come from the memory latency (known as the *memory wall* figure 1.1b), that restricts the scalability of such memory-bounded

Figure 1.1: The Memory Wall describes the increasing gap between CPU performance and memory performance. As this latency gap grows, any irregular application pays a higher and higher performance cost on modern processor architectures. Figures from [38]

algorithms. This performance bottleneck is evident in the historical trends in Figure 1.1a. Over the last 20 years, capacity and bandwidth have followed the scaling of Moore's law, improving 128x and 20x respectively. However, latency has only improved about 30% since 1999. A memory access can take anywhere from 100 to 200 CPU cycles - equivalent to the execution of 100s of instructions. The most common solution to the memory latency problem is the use of extensive *cache hierarchies* that occupy up to 80% of a typical processor die area. This latency mitigation approach relies on data (spatial and temporal) and instruction localities. *Multithreaded execution* [85, 122] has been proposed as an alternative approach that relies on the masking of memory latency by switching to a ready but waiting thread when the currently executing thread encounters a long latency operation, such as a main memory access. Several different multithreading models (simultaneous, fine-grained temporal, coarse-grained temporal) have been proposed along these. They can be distinguished by how close in time instructions from different threads may be executed. In this thesis, the focus will be on coarse-grained temporal multithreading.

Despite wide acceptance of caching as a latency mitigation method of choice this thesis explores an alternative approach by supporting multiple outstanding memory requests from various independent threads. This multithreading architecture is implemented on FPGAs and optimized to process relational database workloads. The design is similar to the multithreading approach used in the SUN UltraSPARC architecture (for example, the UltraSPARC T5 [56] can support eight threads per core and 16 cores per chip). However, because our FPGA implementation is able to support deeper pipelining and custom threads with extremely small contexts, it can maintain thousands (instead of tens) of outstanding memory requests and hence drastically increases concurrency and therefore throughput. Furthermore, the multithreaded execution maximizes the utilization of the available memory bandwidth. Adding to the complications of achieving performance is the proliferation of multicore, many-core, and highly parallel hardwares. No longer is it good enough to simply write efficient single threaded CPU code. If programmers aren't targeting parallelization, they miss out on the resources that modern architectures are providing. The next generation CPU release will most likely have more parallelism advancements than any clock frequency gains. In the world of FPGAs, implementing a single compute engine is not enough for any real performance. Designs need to replicate and use as much area as possible. Parallelization is the way to win modern performance.

In this dissertation, we will look at all of aforementioned issues. We will start by looking at the growth of tools in the FPGA space that try to extract parallel solutions from High Level software code. And we'll also look at the limitations of these tools Then we show how to exploit this massive multithreading to break through the memory wall and provide performance for irregular applications. We also describe the use of CAMs (Content Addressable Memories) as synchronizing caches for hardware multithreading. We demonstrate and evaluate this mechanism by implementing multithreaded datapaths for Breadth First Search, Hash-Join, and Group-By Aggregation. Synchronization between concurrent threads is typically implemented using expensive in-memory locks that are accessed via atomic operations. CAMs allow us to move the lock on chip, increase the multithreading, and achieve better performance. Given their irregular memory nature, these algorithms incur poor spatial locality, thus traditional CPU approaches rely on vast caches to attempt to alleviate the latency penalty. Since an FPGA takes an alternative approach it requires massive parallelism to compete with the CPU's order of magnitude faster clock frequency.

### Chapter 2

### Background

This thesis focuses on irregular algorithms for data analytics. This section presents some general background needed to understand the algorithms that will be implemented. We first give a general overview of multithreading since it is such an overloaded word with several architectural meanings. After covering the models we discuss several architectures that implement each style. We then cover the MT-FPGA execution model and how we implement our hybrid of SMT and coarse-grained temporal multithreading. Finally we'll cover the growth of FPGA heterogeneous computing, the Convey HC-2EX architecture, implementing CAMs on FPGAs, and finally the use of FPGAs for database query processing.

### 2.1 Multithreaded Architectures

The goal of a processor is to fully utilize all hardware resources in any given cycle. However, many times instructions have data dependencies and they cannot execute until all dependencies are met. Compilers can do some work reordering instructions to

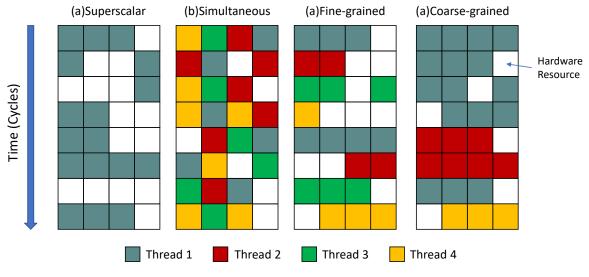

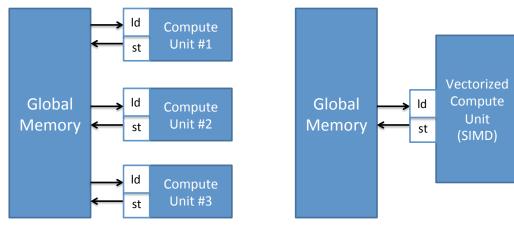

Figure 2.1: Various multithreading models

minimize delay slots in a stream of instructions. And the hardware in the processor can further expand on this by issuing instructions out of order and letting several instructions try to acquire as many dependencies concurrently as possible. However, even with all this advanced instruction scheduling there are often still delay slots to be found.

Multithreaded execution tries to get around this problem by filling slots with instructions from independent threads. Figure 2.1 shows schedules under different multithreading techniques. In the traditional superscalar processor(figure 2.1a), several instructions in a single thread are scheduled to fill available issue slots. Some cycles will be able to use all resources, but sometimes pipeline bubbles are inevitable. Many modern processors with out-of-order superscalar architectures like the IBM Power and Intel Skylake feature support for simultaneous multithreading (SMT) (figure 2.1b). SMT maintains multiple independent threads active in a given core and will take instructions from each thread and issue them to execution units as available. Since each thread is maintained in an active state, there is the benefit that there is no context switching. However, it comes at the cost of increased complexity in the hardware and increased pressure on hardware resources. Each thread may be in a completely different address space and they may keep thrashing local cache and register resources. Extracting peak performance requires diligent effort on the programmer to make sure threads are grouped together wisely.

#### 2.1.1 Temporal Multithreading

In contrast, the fine-grained threading model(figure2.1c) is rather simple. The processor is built around the concept that every thread will be swapped out in a fixed interval, e.g. every cycle. Then, you can hide delay slots by having as many threads as the longest stall in the system. If the current instruction causes a stall, it doesn't matter because the processor is swapping in a new thread and this thread won't be executing for n cycles and the data dependency will already be filled. This model provides high throughput since it is always rotating threads and also provides deterministic, easy to understand behavior. However, this comes at the expense of individual thread performance. Each thread is getting kicked out even if the current instruction won't cause a stall. In fine-grained multithreading with n threads, Compute heavy code with m stall free instructions will take n \* m cycles to execute instead of the m cycles it would take on a traditional pipeline.

Finally, the coarse-grained multithreading model (figure2.1d) tries to take the simpler model of fine-grained and provide better single threaded performance. Instead of swapping threads out in fixed intervals, coarse-grained multithreading only swaps threads out when an instruction triggers a long-latency operation (e.g. memory request). In this case, a thread can continue to make progress while it has instructions to execute. When it needs to wait for data, it can wait in buffers while other threads progress. Single-threaded performance is restored, however, it is at the cost of non-determinism and higher conflicts in shared resources. Coarse-grained multithreading must also maintain enough threads to hide the latency of the requests.

Both fine-grained and coarse-grained multithreading fall in a class called temporal multithreading because they have the idea of using multithreading to hide the time of longrunning operations.Because of this, both have the property that they need significantly more threads than the SMT model. SMT threading needs a number of threads relative to the amount of execution units in the core. The other two models require a number of threads relative to the length of the memory latency. And as we saw in the introduction, the memory wall has been growing for decades, continually pushing up the latency. Between the two classes there is a trade-off of less threads and complicated cores for SMT, and order of magnitude more threads but simpler cores for temporal.

#### 2.2 Latency Masking Multithreaded Architectures

In the early 90s the Tera Corporation, built the Tera MTA. The MTA design consisted of 256 processors sharing 64 GB of memory organized as a distributed NUMA architecture. Its interconnection network allowed better scaling to a larger number of processors. It also forced instruction requests through a shared cache lowering the network traffic. Custom processors supported the issuing of one memory request per thread per cycle. The maximum memory latency from any processor to any memory module was 128 cycles. Each processor could support up to 128 active threads. The MTA design [18] was later evolved into the Cray XMT. While the MTA had only 256 processors the XMT machine could support up to 8,192 processors, but the largest ones built had 512 processors. The shared memory was also increased from 1 TB to 128 TBs for the MTA, and the clock speed was improved from 220 MHz to 500 MHz.

### 2.3 MT-FPGA Execution Model

MT-FPGA (Multithreading on FPGAs) [66] is an execution model that combines the memory masking ability of multithreaded execution with a customized data path. This

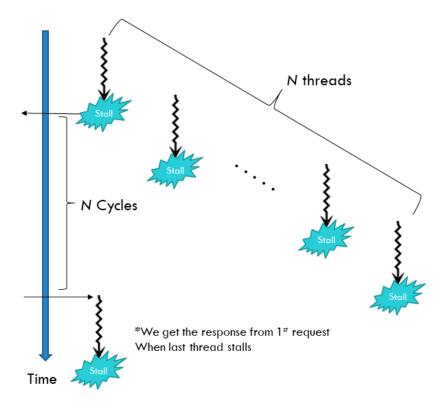

Figure 2.2: Hiding Memory Latency

execution model suspends the thread as soon as it performs a long latency read and a waiting ready thread is given the chance to execute. It performs decoupling by buffering the returned data in the order it was requested. This execution model exhibits following advantages:

- 1. Can support hundreds of outstanding memory requests, hence massive parallelism

- 2. Full utilization of the datapath

- 3. The state of the thread is extremely small, and can therefore cater to more number of pending threads, stored on a FIFO.

A recent tool called CHAT uses the MT-FPGA model. This compilation tool generates customized hardware support for multithreaded execution on FPGAs and claims to ease the hardware development effort for complex irregular kernels. Using just one accelerator FPGA, CHAT shows a speed-up of up to 50x over a single Intel Xeon on simple irregular kernels. Similarly, a database hash-join system demonstrated in [64] is also designed using a MT-FPGA model. Throughput results show a speedup between 2x and 3.4x over the best multi-core approaches with comparable memory bandwidths on uniform and skewed datasets.

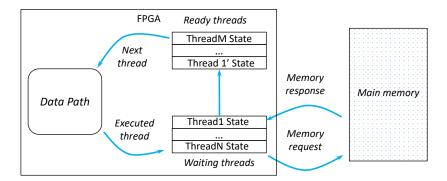

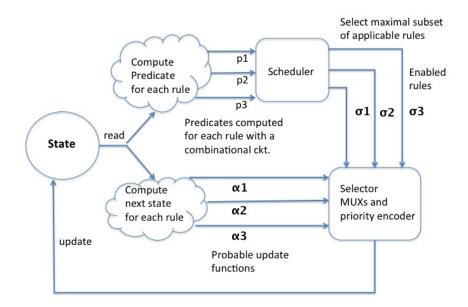

Designing an engine that supports enough threads to hide latency like Figure 2.2 follows a simple model. The high level idea of the model can be seen in Figure 2.3. The compute can be viewed as the datapath block. A thread continues to execute until it needs memory. At this point, the thread will issue the request and move itself into the *Waiting threads* FIFO. Because the hardware guarantees in memory responses, we know that the next response must belong to the thread at the front of the FIFO. A memory response will add the data to the threads state and the thread will move to the *Ready threads* FIFO and

Figure 2.3: MT-FPGA Architecture Model

wait until the datapath reactivates the thread. Since these datapaths are pipelined, we can activate a thread every cycle as long as there are no memory threads. And, the pipelined datapath means we can design the compute only thinking about one thread moving through each state. We don't need to worry about synchronization unless there are shared resources. And in that case, we can use a CAM, as this thesis will show later.

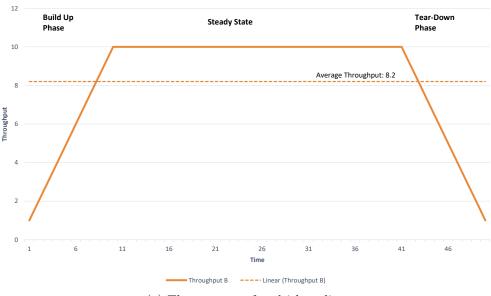

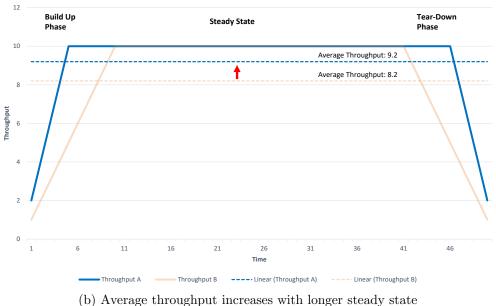

The achievable throughput in this model is demonstrated in Figure 2.4. In Figure 2.4a shows the 3 states of the MT-FPGA model states: Build-up, Steady, and Tear Down. In the Build-up state, threads are getting started and begin issuing requests. Since we do not yet have enough threads making requests, the throughout will be less than the peak bandwidth. Once execution has fully started we transition to the steady state. In the steady state, threads issue requests every cycle and memory is responding with new data every cycle. In this state the throughput is exactly the peak bandwidth since memory is working every cycle. As execution begins to wind down, we transition to the tear down state. Threads finish their work and terminate and we no longer have enough threads to mask latency. In this state, throughput begins dropping as we see more latency. The overall throughput of the full execution is simply the average throughput of all three stages.

(a) Three stages of multithreading

(b) Average throughput increases with longer steady state

Figure 2.4: Execution in the MT-FPGA model has 3 states: Build-up, Steady, and Tear Down. In the build up phase, threads are just getting started and issuing requests so we are not yet masking latency. In the steady state, a thread issues a request every cycle and we receive a response every cycle. in the Tear-Down stage, we start losing masking as threads terminate. The overall throughput is the average of these three stages Figure 2.4b shows why this simple model works so well. As we increase the time the system stays in the steady state, our average throughput will continually increase and approach the full system bandwidth. And the more data the system needs to process, the easier it is to maximize the time in the steady state. This model pairs well with the continued growth of the Big Data era where queries are now running on Terabytes of data. The other benefit of this model is that it works independent of regular or irregular memory access patterns. As long as the engine issues requests every cycle, the throughput will approach the peak bandwidth of the system.

### 2.4 FPGA Heterogeneous Computing

FPGA architectures have evolved from their early stages (supporting simple 8bit logic operations), into large logic arrays capable of concurrently executing multiple complex instructions. They have historically been used as off-chip accelerators where CPUs can offload compute intensive workloads, and read back the results. However, in recent years the FPGA has been trending closer and closer to the CPU. Xilinx currently offers a Zynq [136] line of chips that couples the FPGA's reconfigurable fabric with an ARM processor, and Intel's recent acquisition of Altera suggests this trend will continue. However, it is currently still more common to see the FPGA connected with the CPU over a PCIe bus. Microsoft Research incorporated multiple Stratix-V FPGAs into a 48 node server that was used to accelerate the Bing search engine [110]. Alpha Data announced a CAPI environment, which allows Xilinx All Programmable devices to connect with IBM Power8 architectures [11]. Convey Computers, Maxeler Technologies, and Pico Computing are all companies currently offering FPGA platforms over PCIe, which have been actively used in the research community to show acceleration and power savings compared to CPUs and GPUs [64, 37].

Different FPGA architectures are optimized for various use cases: HPC computations, database workloads or packet processing. The designs proposed in this paper utilize only the off-chip memory interface, which makes them general enough to be ported between most currently available FPGA platforms. For simplicity we choose only one platform, the Convey-WX, to implement and run all our designs. The Convey architecture offers a shared global memory space between hardware and software, which eliminates any variability due to the memory architecture and allows us to do direct performance comparison.

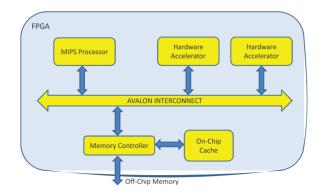

### 2.5 Convey HC-2ex Platform

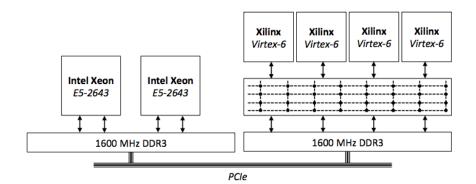

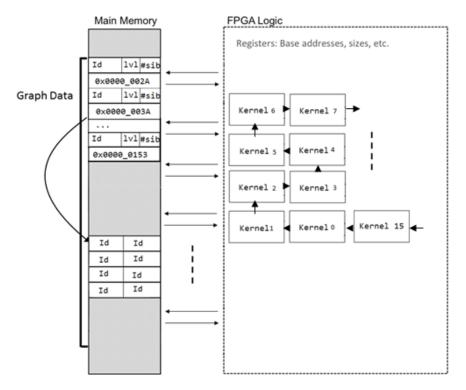

The Convey HC-2ex is a heterogeneous platform that offers a shared global memory space between the CPU and FPGA regions. As shown in Figure 2.5a the memory is divided into regions connected through PCIe with portions closer to the CPU, and portions closer to the FPGAs. The software region has 2 Intel Xeon E5-2643 processors running at 3.3 GHz with a 10 MB L3 cache. In total the software region has 128 GB of 1600 MHz DDR3 memory. The system has a peak memory bandwidth of 51.2 GB/s.

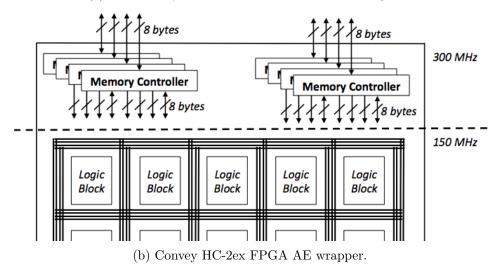

The hardware region has 4 Xilinx Virtex6-760 FPGAs connected to the global memory through a full crossbar. Each FPGA has 8 64-bit memory controllers running at 300MHz (Figure 2.5b). The FPGA logic cells run in a separate 150 MHz clock domain to ease timing and are connected to the memory controllers through 16 channels. These

(a) The Convey HC-2ex software and hardware regions.

Figure 2.5: The Convey HC-2ex architecture. Separation into software and hardware regions in shown in (a). In hardware region each FPGA has 8 memory controllers, which are split into 16 channels for the FPGA's logic cells as shown in (b).

memory channels provide a highly parallel 8,192 simultaneous outstanding requests. The hardware region has 64 GB of 1600 MHz DDR3 RAM. Each FPGA has a peak memory bandwidth of 19.2 GB/s.

### 2.6 CAMs on FPGA

A CAM (also known as an associative memory), is an array that can perform efficient entry-matching (i.e. answer membership queries). Its operation is the inverse of a Random Access Memory (RAM): when presented with a *search word* the CAM returns all the locations whose content matches that word. Each CAM bit consists of a flip-flop with a comparator matching it to the corresponding bit in the search word. The outputs of all the bit positions in a word are ANDed to generate the (mis)match for that word. The CAM's ability to perform a search in unit time comes at a high cost of area, energy and long clock cycle time (due to the long wires for the bit-wise AND and propagating the search word to all the entries)

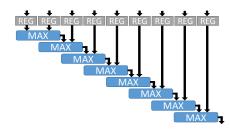

As the number of entries in the CAM increases, the achievable clock frequency of the circuit drops. This limitation either restricts the size of the CAM or increases the number of cycles it takes to perform an update operation. Nonetheless, CAMs have proven to be very useful in domains such as networking (e.g. implementing an IP table in a network router). Recently we explored how CAMs can be used to accelerate the breadth first search algorithm [131].

In a streaming environment CAMs can maintain a cache of recently seen unique items and allow quick access to them without stalling the pipeline. This fast cache lookup mechanism can also be used as a fine-grained address-based synchronization primitive, which avoids long latency trips to main memory and does not require special hardware. Consider the case when a CAM is assigned to guard a particular memory partition. It can be configured to hold the addresses of the values that need synchronized access. If all memory requests within a partition are first submitted to the CAM, before being routed to the memory, the accesses to identical addresses are serialized locally in the CAM. In this case a CAM entry serves as an exclusive lock, which gets released (flushed from the CAM) after the request(s) completion. In [8] we discuss how to use this approach for synchronization in the multithreading group-by aggregation algorithm.

To the best of our knowledge all previous FPGA implementations relied on specialized platform features to provide synchronization primitives. In our previous work [64] we used atomic operations provided by the now discontinued Convey MX architecture [45]. Each word in memory maintains a locking bit that can be set by a memory instruction. The Convey development kit provides test and set instructions that can be executed from the FPGA to lock the memory location while the operation is executed. Leveraging CAMs for synchronization increases the portability of our design. This moves all synchronization operations internal to the FPGA, and can be done on any architecture. In addition, this design provides more selective fine-grained synchronization primitives in comparison to the Convey-MX, which places a lock on all FPGA-memory communication channels.

It was shown that implementing fully-associative matching logic for CAMs on both Altera and Xilinx FPGAs introduces a 60x overhead compared to regular BRAMs [139]. This drawback makes implementing large CAMs on reconfigurable fabrics notoriously hard. Dhawan et al. [51] explored various designs of CAMs and introduced a trade-off between CAM size and update time.

### 2.7 Query Processing on FPGAs<sup>1</sup>

Many research works in the early 1980s were dedicated to the design and architecture of *database machines* - specialized hardware, designed solely for the purpose of storing and processing large amounts of data. These architectures were utilizing parallel data processing by tightly coupling processing units with disk-based storage. The stagnated growth of disk bandwidth coupled with the continuous increase of storage density implied that data management systems were mostly IO bound. At the same time the rapid performance advances of off-the-shelf processors (due to Moore's law) made the database machine very cost-ineffective [27]. This allowed a handful of processors to operate on a large number of parallel disk I/O operations thus avoiding the rigid pairing of storage and compute units. The interest gradually shifted from intra-node database machine-style parallelism to shared-nothing systems, providing effective easy to scale inter-node parallelism [50, 49]. The depletion of the processing frequency growth finally discontinued the "free ride" on performance scaling. Abundance of cheap main memory diminished the role of I/O-related overhead as a main bottleneck. Nevertheless, the growing gap between memory access latency and the processor's computational capabilities ("memory wall") brings up the data access overhead, but on a different level ("memory is the new I/O"). At the same time, the limited bandwidth of current network technology has restricted the scaling potential of the shared-nothing systems. The aforementioned hardware trends as well as The availability of new generation of data processing hardware (GPUs, FPGAs, ASICs) revived the interest in specialized hardware-accelerated database systems. Recently several research projects

$<sup>^1\</sup>mathrm{This}$  section worked on collaboratively with colleague Prerna Budhkar

proposed building hybrid CPU-GPU systems [141, 29, 61, 126, 58]. These systems are deployed on a traditional CPU architecture, but use the GPUs as a co-processor to accelerate easy-to-parallelize parts of the query processing.

Several academic projects have worked towards simplifying the use of custom hardware for query processing. For instance, the Glacier library [101] implements a component library that generates query-specific FPGA circuits for various streaming queries. This approach is suitable for scenarios with few queries that are known in advance. Queries that fall under typical stream processing applications run longer which justifies invoking a timeconsuming synthesis process for every new query. The synthesis time to build an engine is high, and needs to be amortized over many runs to be practical. The technique has been shown useful for event processing systems like high frequency trading [115]. The Q100 [134] architecture is a fixed platform with many ASIC database processing units. A query stream is scheduled through the necessary units. Resources may go unused for a given query, but the platform avoids long build times.

Netezza [75] is a complete DBMS that uses FPGAs as a filter between the hard disk and main memory. Customizable queries are sent to the FPGAs which utilize their close proximity to the hard disk to quickly filter relations before sending them to memory. The platform tries to reduce the costly data transfers from disk to main memory [119]. The trade off for this approach is that all requests must start on disk. In-memory databases cannot leverage the addition hardware FPGAs. Another full DBMS, Kickfire [81], uses FPGA hardware accelerators connected through either PCIe or hyper transport. It defines various database operations as HARP logic that consists of a hardware circuit and a large memory systems. All queries are analyzed by Teradatas C2 software, which decides if it should handle the job itself, send it back the the DBMS, or offload it to HARP logic. The customized hardware supports many common relational database operations [28, 71, 94]

### Chapter 3

# High Level Language Tools for Reconfigurable Computing

This first chapter looks at the flexibility of High Level Synthesis tools. The goal of these tools is to take an algorithm description in a high level language like C/C++ and automatically generate a synthesizable hardware circuit. They provided automated testing facilities for both software and hardware models to try and improve the speed of iterating on hardware design. The hardest, most expensive part of FPGA development tends to be the engineering hours contributed to making and testing the design. Any progress in bringing down development time is extremely beneficial. An insightful webcomic (figure 3.1) on this idea is called "Compiling" by Randall Munroe [137]. As true as waiting for compilation is in the software world, it is painfully more true with hardware. With several projects over the years that took more than 24 hours to build for the FPGA, sometimes creativity wins over productivity.

Figure 3.1: xkcd: Compiling - sometimes there is no other option than jousting in the lab.[137]

While the tools are making tremendous progress, they are not a silver bullet. They generally only work on a subset of the high level language, at the time of this research they only focused on regular compute cores, and they did not support dynamic memory. In this project[132], we look at the tools from the programmer's perspective. How easy it is to describe a design, how easy it is to explore different hardware configurations, and how much of the process to tool automates.

# 3.1 High Level Synthesis and FPGAs

In recent years we have witnessed a tremendous growth in size and speed of FPGAs accompanied by an ever widening spectrum of application domains where they are extensively used. Furthermore, a large number of specialized functional units are being added to their architectures such as DSP units, multi-ported on-chip memories and CPUs. Modern FPGAs are used as platforms for configurable computing that combine the flexibility and re-programability of CPUs with the efficiency of ASICs. Commercial as well as research projects using FPGA accelerators on a wide variety of applications have reported speedup, over both CPUs and GPUs, ranging from one to three orders of magnitude as well as reduced energy consumption per result ranging from one to two orders of magnitude. Application domains have included signal, image and video processing, encryption/decryption, decompression (text, integer data, images etc), data bases [98] [99], dense and sparse linear algebra, graph algorithm, data mining, information processing and text analysis, packet processing, intrusion detection, bioinformatics, financial analysis, seismic data analysis, etc.

FPGAs are programmed using Hardware Description Languages (HDLs) such as VHDL, Verilog, SystemC and SystemVerilog that are used for digital circuit design and implementation. In these languages the circuit to be mapped on an FPGA is designed at a fairly low level: the data paths and state machine controllers are built from the bottom up, timing primitives are used to provide synchronization between signals, the registering of data values is explicitly stated, parallelism is implicit and sequential ordering of events must be explicitly enforced via the state machine. Traditionally trained software developers are not familiar with such programming paradigms. Beyond the program development state, the tool chains are language and vendor specific and consist of a synthesis phase where the HDL code is translated to a netlist, mapping where logic expressions are translated into hardware primitives specific to a device, place and route where hardware logic blocks are placed on the device and wires routed to connect them. This last phase attempts to solve an NP-complete problem using heuristics, such as simulated annealing, and may take hours or days to complete depending on the size of the circuit relative to the device size as well as the timing constraints imposed by the user. The steepness of the learning curve for such languages and tools makes their use a daunting and expensive proposition for most projects.

This paper provides a qualitative survey of the currently available tools, both research and commercial ones, for programming FPGAs as hardware accelerators. We start with a historical prospective on the use of FPGA-based hardware accelerators (Section 3.1.1) showing that the role of FPGAs as accelerators emerged very shorty after their introduction, as glue-logic replacements, in the 1980s. In Section 3.1.2 we discuss the efficiency of the hardware computing model over the stored program model and review the challenges posed by using High-Level Languages (HLLs) as programming tools to generate hardware structures on FPGAs. Related works and five High-Level Synthesis (HLS) tools are described in Section 3, three commercial tools: Xilinx Vivado, Altera OpenCL, Bluespec BSV, and two university research tools: ROCCC and LegUp. We use a simple image filter, dilation, and AES encryption routines to describe the style of programming these tools and explore their capabilities in implementing compiler-based transformations that enhance the throughput of the generated structure (Section 3.3 and Section 3.4). Area, performance and power results for both benchmarks are compared in Section 3.5 and, finally, concluding remarks are presented in Section 3.6. Note: in this paper we report results and compare tools only to the extent allowed by the terms of the user license agreements.

## 3.1.1 A Historical Perspective

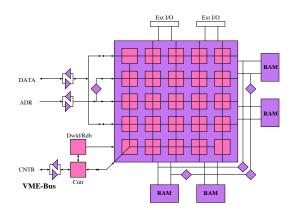

The use of FPGAs as hardware accelerators is not a new concept. Very shortly after the introduction of the first SRAM-based FPGA device (Xilinx, 1985) the PAM (Programmable Active Memory) [22][127] was conceived and built at the DEC Paris Research Lab (PReL). The PAM  $P_0$  consists of a 5x5 array of Xilinx XC3020 FPGAs (Figure 3.2) connected to various memory modules as well as to a host workstation via a VME bus. It had a maximum frequency of 25MHz, 0.5 MB of RAM, and communicated on a host bus of 8 MB/s. The PAM  $P_{\rm 1}$  was built using slightly newer FPGA, the Xilinx XC3090. It operated with a maximum frequency of 40MHz, 4 MB of RAM, and used a 100 MB/s host bus. It was described as "universal hardware co-processor closely coupled to a standard host computer" [23]. It was evaluated using ten benchmark codes [23] consisting of: long multiplication, RSA cryptography, Ziv-Lempel compression, edit distance calculations, heat and Laplace equations, N-body calculations, binary 2D convolution, Boltzman machine model, 3D graphics (including translation, rotation, clipping and perspective projection) and discrete cosine transform. It is interesting to note that most of these benchmarks are still today subjects of research and development efforts in hardware acceleration. Berlin et al. in [23] conclude that PAM delivered a performance comparable to that of ASIC chips or supercomputers, of the time, and was one to two orders of magnitude faster than software. They also state that because of the PAM's large off-chip I/O bandwidth (6.4 Gb/s) it was ideally suited for "on-the-fly data acquisition and filtering," which is exactly the computational model, streaming data, adopted by most of the hardware acceleration projects that rely on FPGA platforms.

Figure 3.2: Architecture of the DEC PReL PAM  $P_0$

This first reconfigurable platform was rapidly followed by the SPLASH 1 (1989) and SPLASH 2 (1992) [112, 30, 111, 73, 109] projects at the Supercomputer Research Center. Each were linear arrays of FPGAs with local memory modules. They were designed for accelerating string-based operations and computations such as edit distance calculations. The SPLASH 2 was reported to achieve four orders of magnitude speedup, over a SUN SPARC 10, on edit distance computation using dynamic programming.

Table 3.1: Architecture parameters of the SPLASH 1 and SPLASH 2 accelerators

|                | SPLASH 1     | SPLASH 2                |

|----------------|--------------|-------------------------|

| Year           | 1989         | 1992                    |

| FPGA           | XC3090       | XC4010                  |

| 4-LUT/board    | 10,240       | 13,600                  |

| Max. bandwidth | 1  MB/s      | 100  MB/s               |

| Memory/FPGA    | 128 KB       | 512 KB                  |

| Interconnect   | Linear array | Linear array, broadcast |

The PAM and SPLASH projects put the foundation of reconfigurable computing by using FPGA-based hardware accelerators. In the past two decades the density and speed of FPGAs have grown tremendously: the density by several orders of magnitude, the clock speed by just over one order of magnitude. Both of these projects could each be easily implemented on single moderately sized modern FPGA device. However, the main challenge to FPGAs as hardware accelerators, namely the abstraction gap between application development and FPGA programming, not only remains unchanged but has probably gotten worse due to increase in complexity of the applications enabled by the larger device sizes. FPGA hardware accelerators are still beyond the reach of traditionally trained application code developers.

#### 3.1.2 Hardware and Software Computing Models

In this section we discuss two issues that define the complexity of compiling HLLs to hardware circuits: (1) the semantic gap between the sequential stored-program execution model implicit in these languages and (2) the effects of abstractions, or lack thereof, on the complexity of the compiler.

#### Efficiency and Universality

The stored program model is a universal computing model: it is equivalent to a Turing machine with the limitations on the size of the tape imposed by the virtual address space. It can therefore be programmed to execute any computable function. Hardware execution, on the other hand, is not universal unless it has an *attached* microprocessor. It is, however, extremely efficient. Consider an image filter applied on a  $3 \times 3$  pixel window over a frame: the *forall* loop implemented in hardware can be both pipelined (let d be the pipeline depth) and unrolled as to compute multiple windows concurrently, let the unroll

factor be k. In the steady state  $d \times k$  operations are being executed concurrently producing k output results per cycle. On a CPU, the innermost loop of a typical image filter requires 20 to 30 machine instructions per loop body including nine load instructions. Assuming an average instruction level parallelism (ILP) of two, each result takes 10 to 15 machine cycles - which is the ratio of the respective clock speeds of CPUs and GPUs to FPGAs. However, that same loop can be replicated many times on the FPGA achieving a much higher throughput (at least an order of magnitude). Furthermore, the ability to configure local customized storage on the FPGA makes it possible to reduce the number of memory accesses, mostly reads, by reusing already fetched data resulting in a more efficient use of the memory bandwidth and lower energy consumption per task [90]. Hence the higher speedup or throughput observed on a very wide range of applications using FPGA accelerators over multi-cores (CPUs and GPUs). Further details on CPU efficiency for image filters are discussed in Section 3.3.1.

#### Semantics of the Execution Models

CPUs and GPUs are inherently stored-program (or von Neumann) machines and so are the programming languages used on these. Most of the languages in use today reflect the stored program paradigm. As such they are bound by its sequential consistency, both at the language and machine levels. While CPU and GPU architectures exploit various forms of parallelism, such as instruction, data and thread-level parallelisms, they do so circumventing the *sequential consistency* implied in the source code internally (branch prediction, out-oforder execution, SIMD parallelism, etc.), while preserving the appearance of a sequentially consistent execution externally (reorder buffers, precise interrupts etc.). The compiling of a HLL code to a CPU or GPU is therefore the translation from one stored program machine model, the HLL, to another, the machine's Instruction Set Architecture (ISA). In the stored program paradigm the compiler can generate a parallel execution only when doing so is provably safe. In other words when the record of execution can be *proved*, by the compiler, to be either identical or equivalent to the sequential execution. For example, in a single level *forall* loop, any interleaving of the iterations produces a correct result. Also, in a single threaded CPU execution the producer/consumer relationship is not a parallel construct since the semantics imply that all the data must be produced before any datum can be consumed. Hence all the data is stored in memory by the producer loop before the consumer loop starts execution.

A digital circuit, on the other hand, is inherently parallel, spatial, with distributed storage and timed behavior. HDLs (e.g. VHDL, Verilog, SystemC and Bluespec) are arguably the most commonly used parallel languages. In a digital circuit the producer/consumer relation is a parallel structure: the data produced is temporarily stored in a local buffer the size of which is determined by the relative rates of production and consumption. Furthermore, any implementation would be expected to include back pressure and synchronization mechanisms to (1) halt the production before the buffer is full and (2) stall the consumption when the buffer is empty to achieve a correct implementation. Buffering the data is not necessary when compiling individual kernels (e.g. stand-alone filters). However, it becomes a necessity, and often a major challenge, when compiling larger systems. Consider data streaming through a series of filters: buffers and back-pressure are necessary to

| Table 3.2: Features and | characteristics of \$ | Stored Program | and Spatial                           | computation models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|-----------------------|----------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                       |                | · · · · · · · · · · · · · · · · · · · | The second |

|             | Stored Program                   | Spatial Computing             |  |

|-------------|----------------------------------|-------------------------------|--|

| Storage &   | Central, large, virtual address  | Distributed, small, physical. |  |

| data access | space. Multi-level caches        | Streaming data. Limited       |  |

|             |                                  | caching. No virtual memory    |  |

| Parallelism | Dynamic - separate ILP, DLP,     | Static - integrated ILP, DLP, |  |

|             | TLP                              | TLP                           |  |

| Sequencing  | Central, static, sequentially    | Data-flow, asynchronous       |  |

|             | consistent                       |                               |  |

| Data-Path   | Pre-designed, one size fits all. | Customized, very deep         |  |

|             | Dynamic data dependencies        | pipelines. No dynamic data    |  |

|             |                                  | dependencies                  |  |

hold the data between filters. Automatically inferring efficient buffering schemes without user assistance in the forms of pragmas or annotations is a major challenge.

Edwards [53] makes the case that C-based languages are not well suited for HLS. The major challenges described in the paper for C-based languages apply to most HLLs. These challenges are the lack of: (1) timing information in the code, (2) size-based data types (or variable bit length data types), (3) built-in concurrency model(s), (4) local memories separated from the abstraction of one large shared memory. While all these points are valid, the main attraction of C-based languages is familiarity. Most HLS tools using Cbased languages provide workarounds for one or more of these obstacles as described in [53].

The abstraction and semantic gaps between the hardware and software computing models are summarized in Table 3.2. Translating a HLL to a circuit requires a transformation of the sequential to a spatial/parallel, with the creation of custom sequencing, timed synchronizations, distributed storage, pipelining, etc. The storage in the von Neumann model is abstracted in a single large virtual address space with *uniform* access time (in theory). The spatial model is better served with multiple local small memories. The parallelism in the von Neumann model can be dynamic: threads are created and complete relinquishing resources. In hardware every thread must be provisioned with resources statically. The software model relies on an implicit sequential consistency where all instructions execute in program order and no instruction starts before all the previous instructions have completed execution. The hardware execution is data flow driven.

Raising the abstraction level of FPGA programming to that of CPU or GPU programming is a daunting task that is yet to be fully completed. It is of critical importance in the programming of accelerators as opposed to the high-level design of arbitrary digital circuit, which is the focus of high-level synthesis. Hardware accelerators differ from general purpose logic design in one important way: the starting point of logic design is a device whose behavior is specified by a hardware description code implemented in a HDL such as VHDL, Verilog, SystemC, SystemVerilog, or Bluespec. The starting point of a hardware accelerator is an existing software application a subset of which, being frequently executed, is translated into hardware. That subset is, quasi by definition, a loop nest. Hopefully that loop nest is parallelizable and can therefore exploit the FPGA resources. By focusing on loop nests, the task of compiling HLLs to FPGAs is simplified and opportunities for loop transformations and optimizations abound. The ROCCC compiler takes this approach and is described later in this paper.

# 3.2 Related Work

As the number of tools supporting HLS for FPGAs has increased so has the number of surveys comparing and contrasting such tools. However, the rapidly shifting landscape of HLS tools for reconfigurable computing makes most endeavors obsolete within a few years. A description of the historical evolution of HLS tools, starting with the pioneering work in the 1970s can be found in [92]. The authors offer an interesting analysis of the reasons behind the successes and failures of the various generations of HLS tools. While the survey is not focused on HLS tools for FPGAs, it does mention several FPGA-specific tools, such as Handel-C, as well as general HLS tools that could be used for FPGAs.

The major research efforts in compiling high-level languages to reconfigurable computing are surveyed in [36]. The paper offers an in-depth analysis of the tools available at that time. AutoESL is described in [44]. The paper also provides an extensive survey of HLS in general and of tools specifically for FPGA programming. In [54] the authors reviewed six high level languages/tools based on programming productivity and generated hardware performance (frequency, area). User experience of using the targeted languages is recorded and normalized as a measure of productivity in this study. However, most of the tools evaluated in this work are no longer supported by their developers.

An extensive evaluation of 12 HLS tools in terms of capabilities, usability and quality of results is presented in [93]. The authors use Sobel edge detection to evaluate the tools along eight specific criteria: documentation, learning curve, ease of implementation, abstraction level, data types, exploration, verification and quality of the results. Daoud et al. [48] survey past and current HLS tools.

#### 3.2.1 Xilinx Vivado HLS