### UC Riverside UC Riverside Electronic Theses and Dissertations

#### Title

Efficient Execution of Scientific Applications on Heterogeneous Architectures

#### Permalink

https://escholarship.org/uc/item/8kn3j3pd

#### Author Belviranli, Mehmet Esat

# Publication Date 2016

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Efficient Execution of Scientific Applications on Heterogeneous Architectures

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Computer Science

by

Mehmet Esat Belviranli

December 2016

Dissertation Committee:

Dr. Laxmi N. Bhyuan, Chairperson Dr. Rajiv Gupta Dr. Walid Najjar Dr. Nael Abu-Ghazaleh

Copyright by Mehmet Esat Belviranli 2016 The Dissertation of Mehmet Esat Belviranli is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

It is my great pleasure to thank those who made this dissertation possible. I would never have been able to finish it without the guidance of my committee members, my wife, help from friends, and support from my family.

I would like to express my deepest gratitude to my advisor, Dr. Laxmi Bhuyan, for his excellent guidance, caring, patience, and providing me with a pleasant atmosphere for doing research. I am also very grateful to Dr. Rajiv Gupta for his previous contribution and endless help in my research. I would also like to thank Dr. Walid Najjar and Dr. Nael Abu-Ghazaleh for guiding my dissertation, giving precious advice and participating in my final defense committee.

Another person who made this study possible is my wife who always has been with me, giving moral support and taking care of everything on behalf of me when I am busy with my work.

I would also like to thank my dear parents, my brother and my sister. They were always supporting me and encouraging me with their best wishes. I also thank all members from my lab and my collaborators, who were always willing to help, discuss ideas, and give helpful suggestions.

Finally many thanks to all and friends for always being on my side throughout my Ph.D study. Without them, it would have been very difficult. This dissertation includes content published in the following journals and proceedings:

- ACM Transactions on Architecture and Code Optimization (TACO) Special Issue on High-Performance Embedded Architectures and Compilers Volume 9 Issue 4 Article No. 57, January 2013.

- Proceedings of the Sixth International Workshop on Data Intensive Distributed Computing, Pages 29-34.

- Proceedings of the 29th ACM on International Conference on Supercomputing, Pages 25-35.

- Proceedings of the 2016 International Conference on Supercomputing, Article No. 31.

I dedicate my work to the one who has planted the seeds of faith, strength and courage into the deepest trenches of my heart to guide me through the most challenging labyrinths of life...

#### ABSTRACT OF THE DISSERTATION

Efficient Execution of Scientific Applications on Heterogeneous Architectures

by

Mehmet Esat Belviranli

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, December 2016 Dr. Laxmi N. Bhyuan, Chairperson

Today's heterogeneous architectures bring together multiple general purpose CPUs, domain specific GPUs and FPGAs to provide dramatic speedup for many applications. However, the challenge lies in utilizing these heterogeneous processors to optimize overall application performance so that workload completion time is minimized. Operating system and application development for these systems are in their infancy.

In this dissertation, we propose various techniques to improve overall system throughput on heterogeneous systems. We develop run-time and compile-time mechanisms to efficiently distribute the workload between various processors and accelerators, transfer the corresponding data to execute them. We explore various data partitioning, synchronization and scheduling schemes to improve load balance, maximize resource utilization and minimize the execution time. First, we propose a dynamic scheduling mechanism to incorporate all available processing units in the execution of a given parallel loop. Our scheme automatically detects the computation speed of each CPU and accelerator and distributes the workload accordingly during run-time. We, then, focus on improving data transfers over PCI-e bus to further improve the system throughput in the existing of multiple applications sharing a single GPU. We present a framework to exploit automatic transfer/execution overlapping without requiring any modifications to source code.

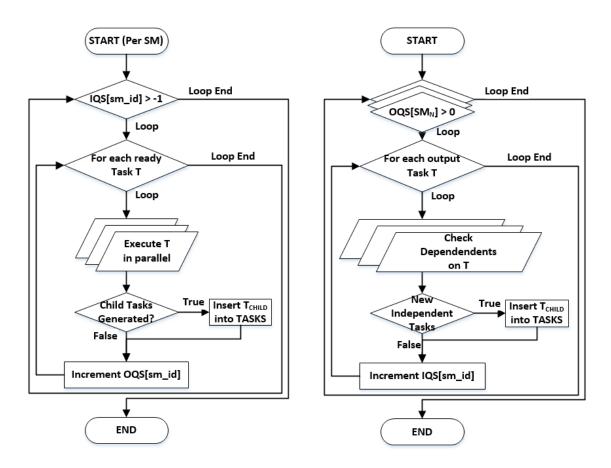

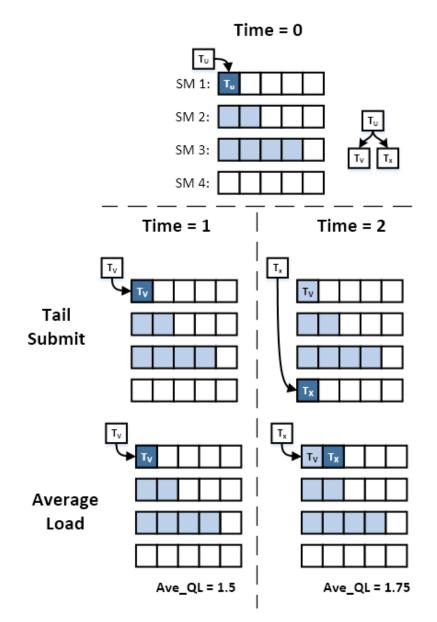

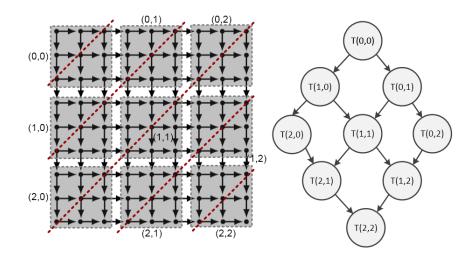

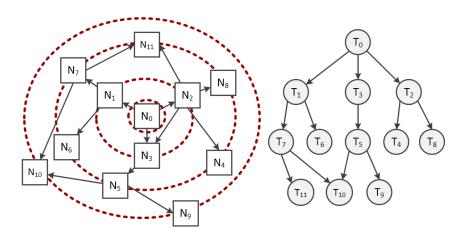

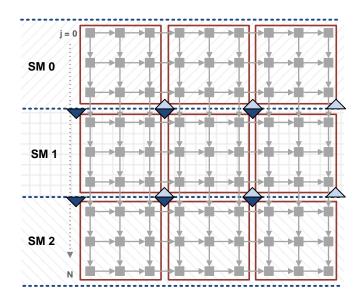

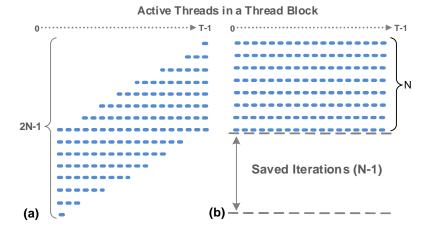

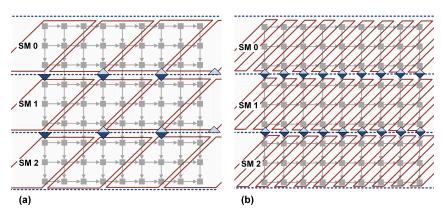

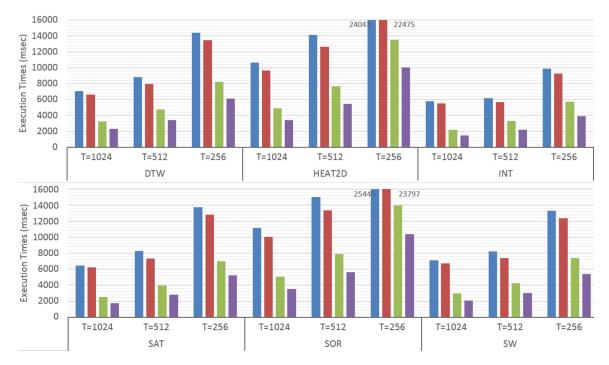

We further improve heterogeneous system efficiency by optimizing in-GPU execution. We find that barrier synchronizations cause a bottleneck in performance. We develop a task based execution scheme that utilizes distributed queues to exploit better cache locality and inter-SM load balance. Finally, we introduce a tile-based wavefront execution technique by removing global barriers and employing a novel peer-SM synchronization mechanism. Through extensive experiments, we observe that our schemes significantly outperforms existing state-of-the-art approaches.

### Contents

| Li       | st of          | Figure          | es                                               | xii             |

|----------|----------------|-----------------|--------------------------------------------------|-----------------|

| Li       | st of          | Tables          | 5                                                | xiv             |

| 1        | Intr           | oducti          | on                                               | 1               |

| <b>2</b> | $\mathbf{Rel}$ | ated W          | Vork                                             | 11              |

|          | 2.1            | Hetero          | ogneous Workload Partitioning                    | 11              |

|          |                | 2.1.1           | Static partitioning                              |                 |

|          |                | 2.1.2           | Dynamic partitioning                             |                 |

|          |                | 2.1.3           | Self Scheduling                                  |                 |

|          | 2.2            | Transf          | fer and Execution Overlapping                    |                 |

|          |                | 2.2.1           | Multi application scheduling                     |                 |

|          |                | 2.2.2           | Automated transfer / execution overlapping       |                 |

|          |                | 2.2.3           | Kernel performance estimation                    | 16              |

|          | 2.3            |                 | SM Synchronization                               | 17              |

|          |                | 2.3.1           | Global Barriers                                  | 17              |

|          |                | 2.3.2           | Inter-SM Communication                           |                 |

|          |                | 2.3.3           | Task Based Execution                             | 18              |

| 3        | Dyr            | namic S         | Scheduling across Heterogeneous Processing Units | 20              |

|          | 3.1            | Introd          | uction                                           | 20              |

|          | 3.2            | Motiva          |                                                  | 23              |

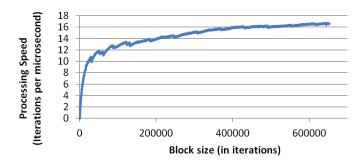

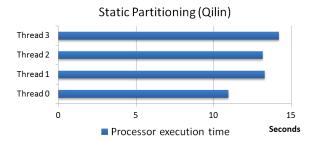

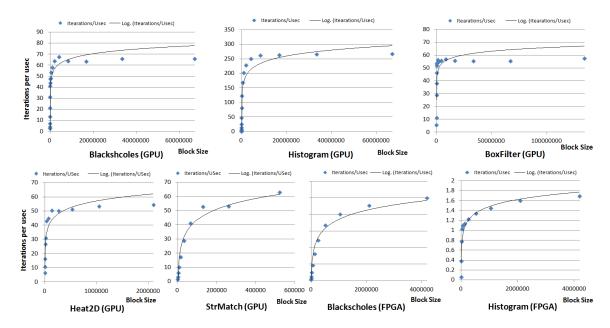

|          |                | 3.2.1           | Effect of Block Size                             |                 |

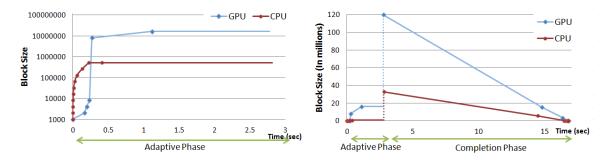

|          |                | 3.2.2           | Computational Rates (Weights)                    |                 |

|          |                | 3.2.3           | Online Training                                  |                 |

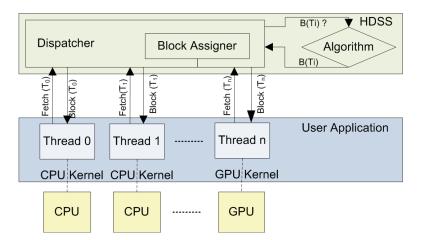

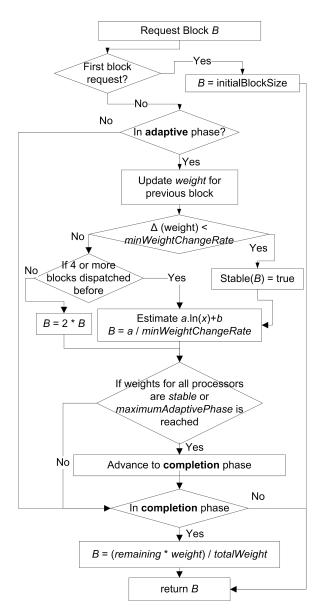

|          | 3.3            | HDSS            | : Heterogeneous Dynamic Self Scheduler           |                 |

|          |                | 3.3.1           | Overview                                         | 27              |

|          |                | 3.3.2           | The Algorithm                                    | 29              |

|          |                | 3.3.3           | Dependency Resolution                            |                 |

|          | 3.4            | Evalua<br>3.4.1 | ation                                            | $\frac{38}{38}$ |

|          |                | 0.4.1           | System Conngutation                              | 00              |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.4.2  | Applications                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

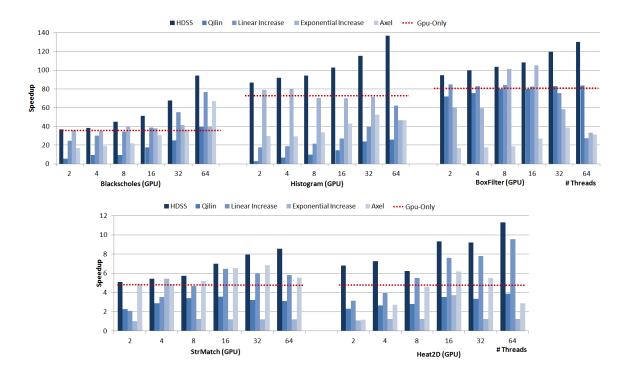

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.4.3  | Algorithms Compared                                                                                                                           |

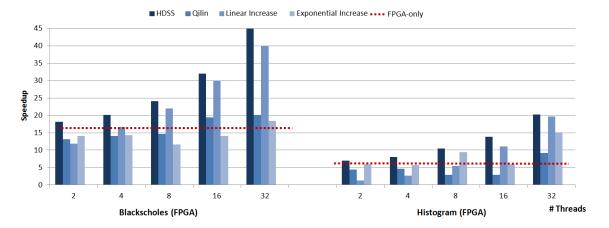

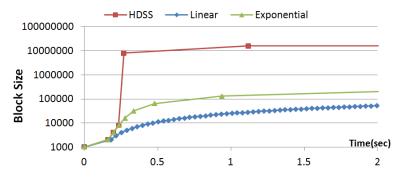

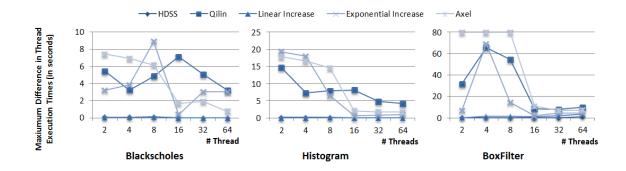

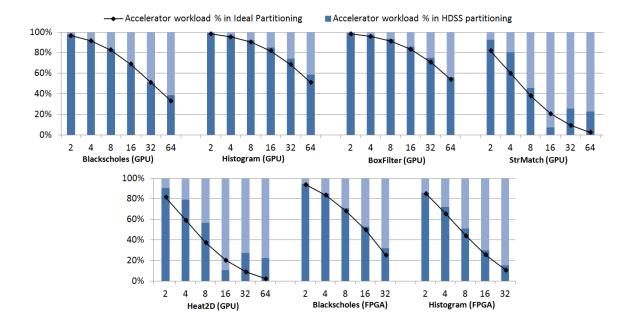

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.4.4  | Results 40                                                                                                                                    |

| <b>4</b> | Dat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | a Tran | sfer and Computation Overlapping 49                                                                                                           |

|          | 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Introd | uction                                                                                                                                        |

|          | 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GPU S  | Sharing in CUDA                                                                                                                               |

|          | 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CuMA   | S: Tasks and Call Ordering                                                                                                                    |

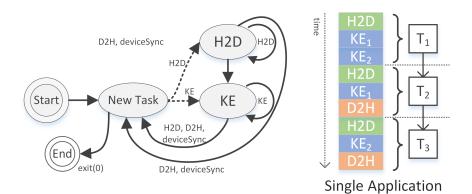

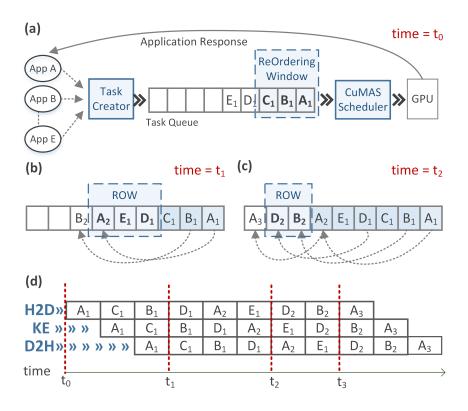

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.1  | CuMAS Tasks                                                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.2  | Re-Ordering Window (ROW)                                                                                                                      |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.3  | Scheduler Invocation                                                                                                                          |

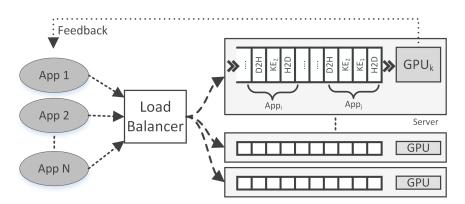

|          | 4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CuMA   | S: Scheduler                                                                                                                                  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4.1  | Scheduling Considerations                                                                                                                     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4.2  | Formulating the Total Execution Time                                                                                                          |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4.3  | Finding a Solution                                                                                                                            |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4.4  | Scheduling Algorithm                                                                                                                          |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.4.5  | Complexity                                                                                                                                    |

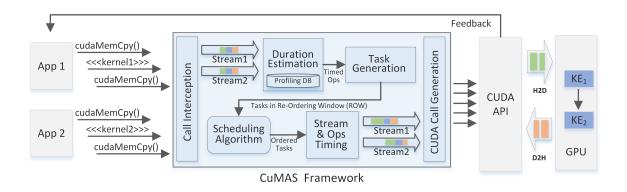

|          | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CuMA   | S: Framework and Runtime                                                                                                                      |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5.1  | Call Interception                                                                                                                             |

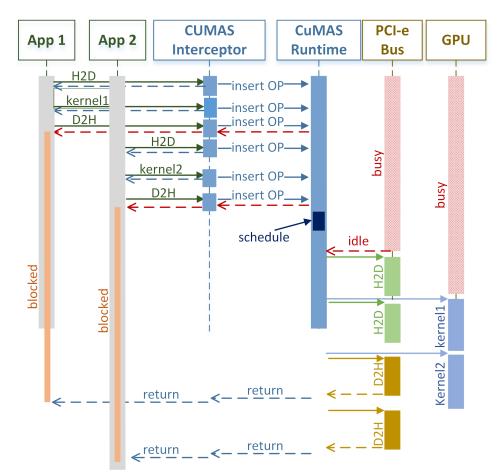

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5.2  | CuMAS Runtime - HW Interaction                                                                                                                |

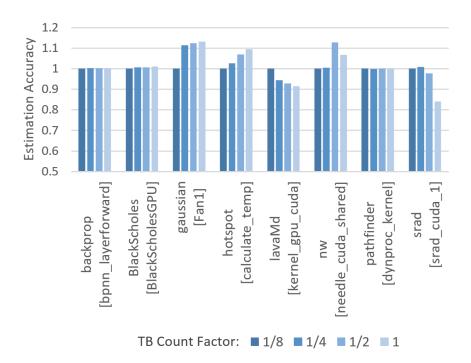

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.5.3  | Duration Estimation & Profiling                                                                                                               |

|          | 4.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Evalua | $ation \ldots \ldots$  |

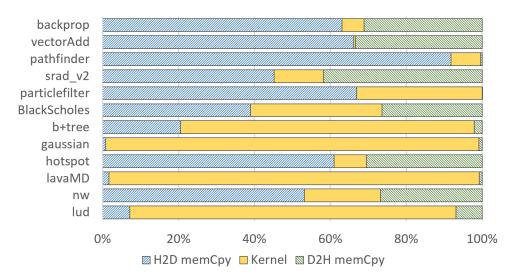

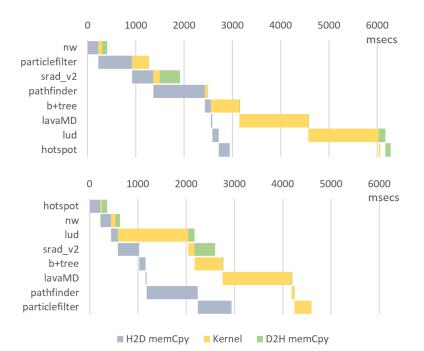

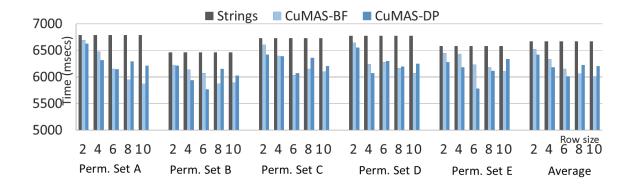

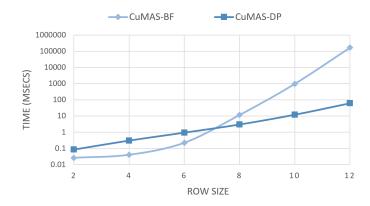

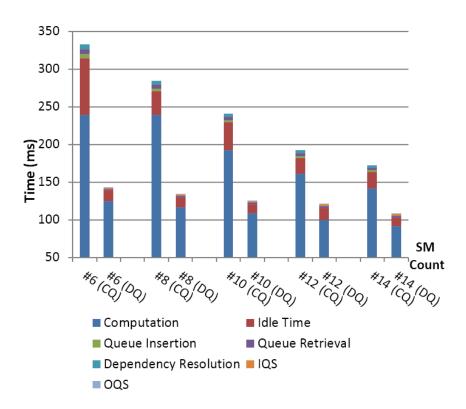

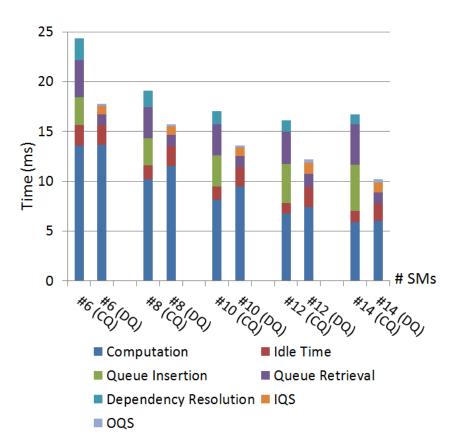

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.6.1  | Execution Time                                                                                                                                |

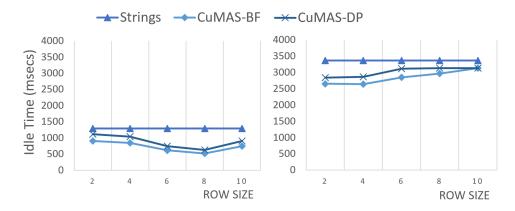

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.6.2  | Resource Idleness                                                                                                                             |

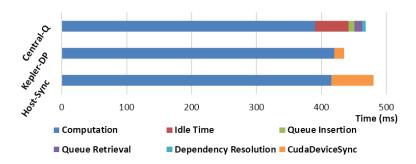

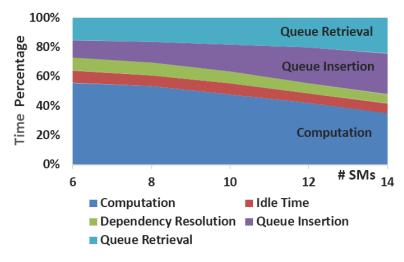

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.6.3  | Scheduling Overhead                                                                                                                           |

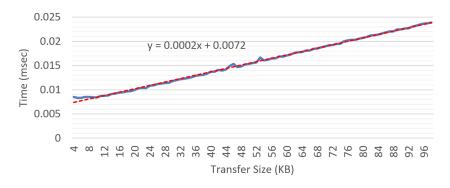

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.6.4  | Data Transfer and Kernel Execution Time Estimation 81                                                                                         |

| _        | The second secon |        |                                                                                                                                               |

| <b>5</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        | d Execution of GPU Applications 84                                                                                                            |

|          | 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        | uction $\ldots \ldots \ldots$ |

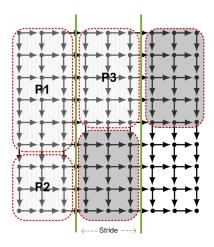

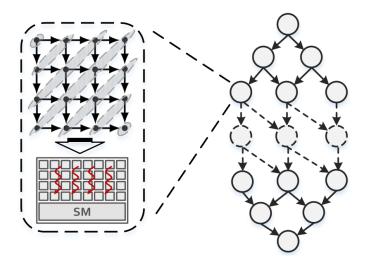

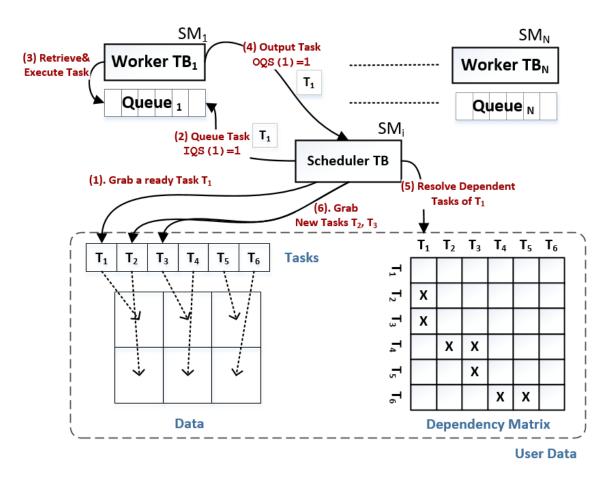

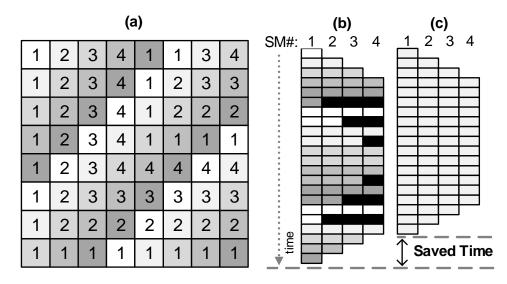

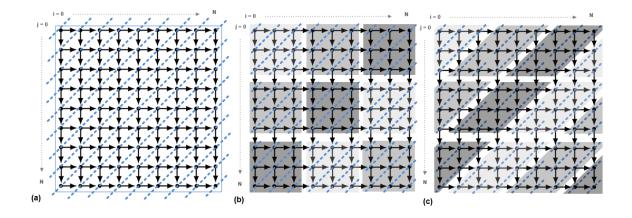

|          | 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -      | adigm shift: Task Based Execution on GP-GPUs                                                                                                  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2.1  | Dependency: An inherent problem of GP-GPU programming 88                                                                                      |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2.2  | Task-based Execution Model    89                                                                                                              |

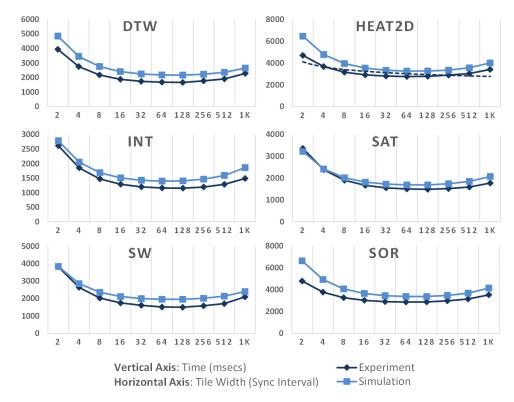

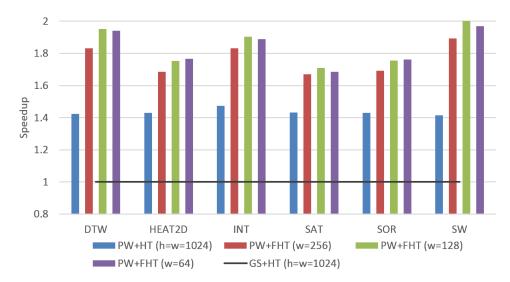

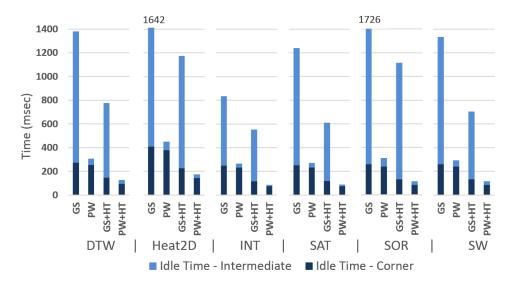

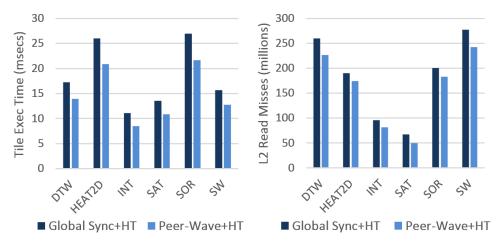

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.2.3  | Possible Approaches                                                                                                                           |